2-46 Service Guide

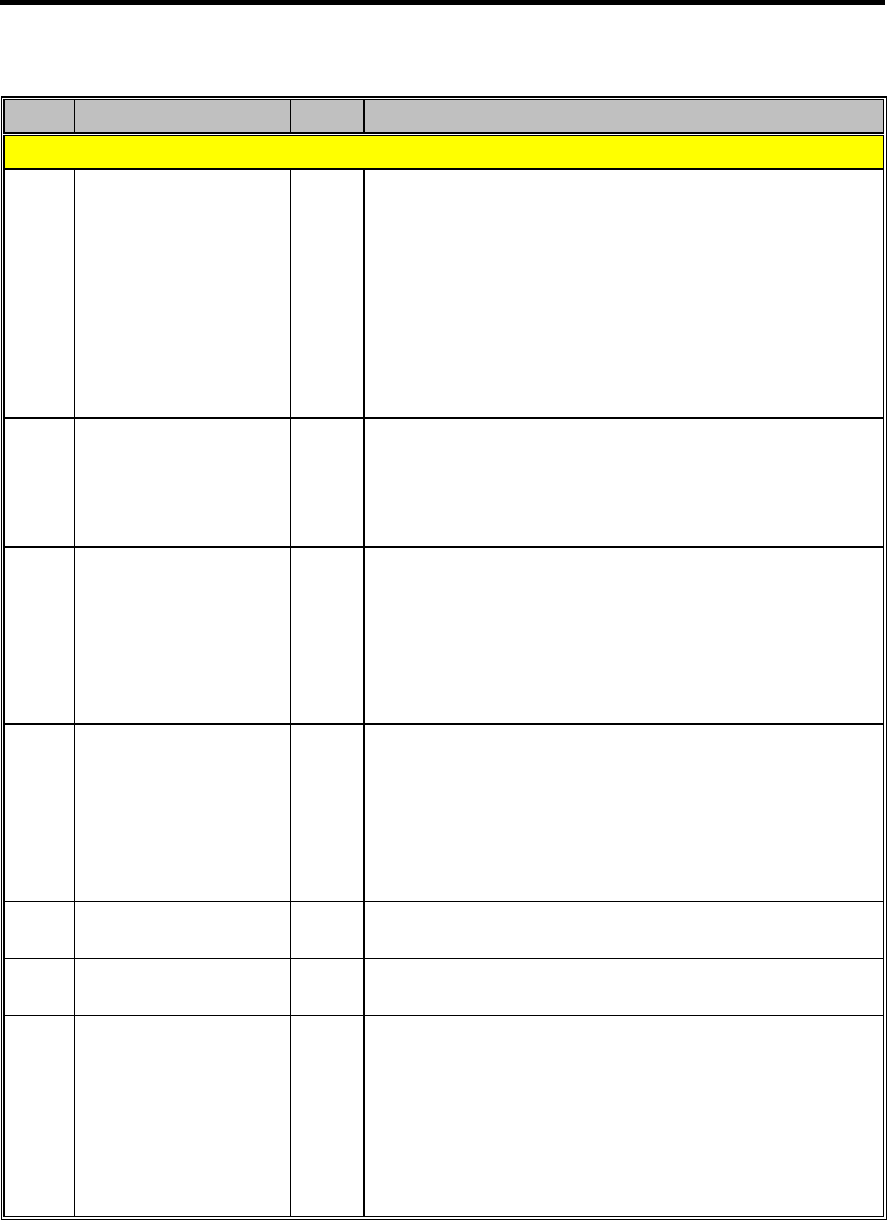

Table 2-10 C&T 65550 Pin Descriptions (continued)

Pin# Pin Name Type Description

PCI Bus Interface (continued)

31 PAR I/O Parity. This signal is used to maintain even parity across

AD0-31 and C/BE0-3#. PAR is stable and valid one clock

after the address phase. For data phases, PAR is stable and

valid one clock after either IRDY# is asserted on a write

transaction or TRDY# is asserted on a read transaction.

Once PAR is valid, it remains valid until one clock after the

completion of the current data phase (i.e., PAR has the same

timing as AD0-31 but delayed by one clock). The bus master

drives PAR for address and write data phases; the target

drives PAR for read data phases.

22 FRAME# In Cycle Frame. Driven by the current master to indicate the

beginning and duration of an access. Assertion indicates a

bus transaction is beginning (while asserted, data transfers

continue); de-assertion indicates the transaction is in the final

data phase.

23 IRDY# In Initiator Ready. Indicates the bus master's ability to complete

the current data phase of the transaction. During a write,

IRDY# indicates valid data is present on AD0-31; during a

read it indicates the master is prepared to accept data. A

data phase is completed on any clock when both IRDY# and

TRDY# are sampled then asserted (wait cycles are inserted

until this occurs).

24 TRDY# S/TS Target Ready. Indicates the target's ability to complete the

current data phase of the transaction. During a read, TRDY#

indicates that valid data is present on AD0-31; during a write

it indicates the target is prepared to accept data. A data

phase is completed on any clock when both IRDY# and

TRDY# are sampled then asserted (wait cycles are inserted

until this occurs).

27 STOP# S/TS Stop. Indicates the current target is requesting the master to

stop the current transaction

25 DEVSEL# S/TS Device Select. Indicates the current target has decoded its

address as the target of the current access

29 PERR# (VCLKOUT) S/TS Parity Error. This signal reports data parity errors (except the

Special Cycles where SERR# is used). The PERR# is

Sustained Tri-state. The receiving agent will drive PERR#

active two clocks after detecting a data parity error. PERR#

will be driven high for one clock before being tri-stated as with

all sustained tri-state signals. PERR# will not report status

until the chip has claimed the access by asserting DEVSEL#

and completing the data phase.