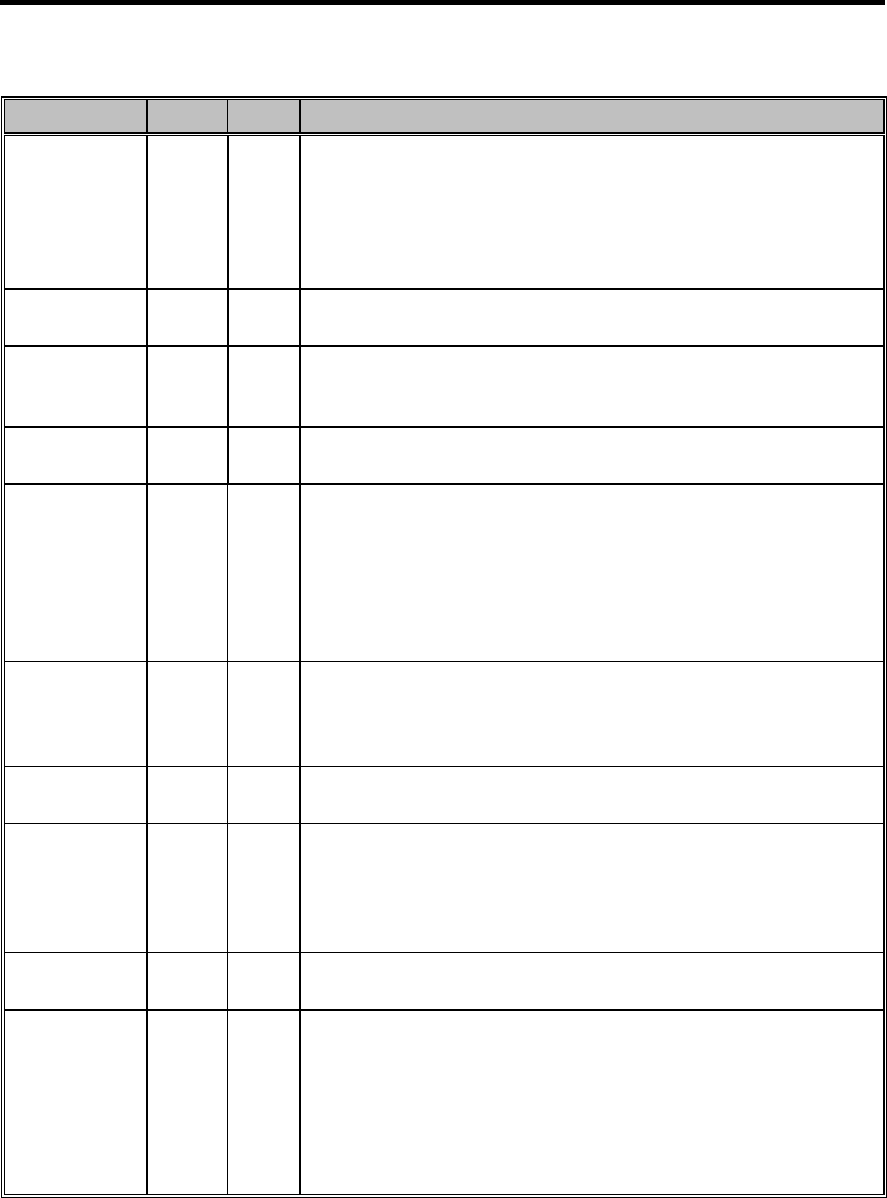

Major Chips Description 2-81

Table 2-14 NS87336VJG Pin Descriptions (continued)

Pin No. I/O Description

DENSEL

(Normal Mode)

46 O FDC Density Select. DENSEL indicates that a high FDC density data

rate (500 Kbs, 1 Mbs or 2 Mbs) or a low density data rate (250 or 300

Kbs) is selected. DENSEL is active high for high density (5.25-inch

drives) when IDENT is high, and active low for high density (3.5-inch

drives) when IDENT is low. DENSEL is also programmable via the

Mode command.

DENSEL

(PPM Mode)

76 O FDC Density Select. This pin offers an additional Density Select

signal in PPM Mode when PNF=0.

/DIR

(Normal Mode)

39 O FDC Direction. This output determines the direction of the floppy disk

drive (FDD) head movement (active = step-in; inactive = step-out)

during a seek operation. During reads or writes, DIR is inactive.

/DIR

(PPM Mode)

78 O FDC Direction. This pin offers an additional Direction signal in PPM

Mode when PNF = 0.

/DR0,

/DR1

(Normal Mode)

42, 43 O FDC Drive Select 0, 1. These are the decoded drive select outputs

that are controlled by Digital Output Register bits D0, D1. The Drive

Select outputs are gated with DOR bits 4-7. These are active low

outputs. They are encoded with information to control four FDDs

when bit 4 of the Function Enable Register (FER) is set. DR0

exchanges logical drive values with DR1 when bit 4 of Function

Control Register is set.

/DR1

(PPM Mode)

83 O FDC Drive Select 1. This pin offers an additional Drive Select signal

in PPM Mode when PNF = 0. It is drive select 1 when bit 4 of FCR is

0. It is drive select 0 when bit 4 of FCR is 1. This signal is active

low.

/DR23 47 O FDC Drive 2 or 3. /DR23 is asserted when either Drive 2 or Drive 3 is

assessed(except during logical drive exchange).

/DRATE0

/DRATE1

(Normal Mode)

50, 49 O FDC Data Rate 0, 1. These outputs reflect the currently selected

FDC data rate (bits 0 and 1 in the Configuration Control Register

(CCR) or the Data Rate Select Register (DSR), whichever was written

to last). The pins are totem-pole buffered outputs (6 mA sink, 6 mA

source).

/DRATE0

(PPM Mode)

85 O FDC Data Rate 0. This pin provides an additional Data Rate signal,

in PPM mode, When PNF=0.

DRQ0

DRQ1

DRQ2

54

31

2

O DMA Request 0, 1, 2. \An active high output that signals the DMA

controller that a data transfer is required. This DMA request can be

sourced by one of the following: FDC or Parallel Port.

When it is not sourced by and of them, it is in TRI-STATE. When

the sourced device is disabled or when the sourced device is

configured with no DMA, it is also in TRI-STATE. Upon reset, DRQ2

is used by the FDC.