2-18 Service Guide

2.3.4 Signal Descriptions

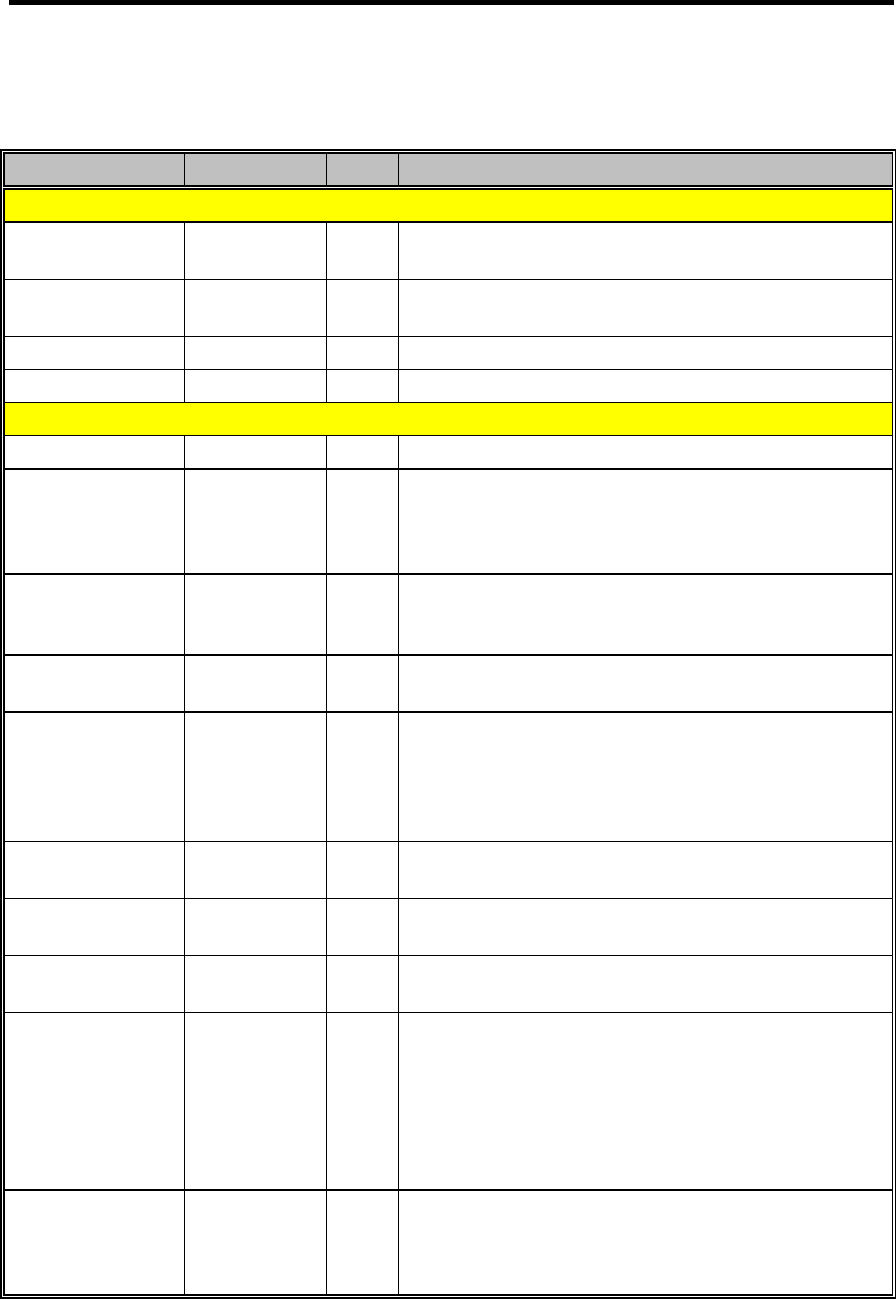

Table 2-3 M1523 Signal Descriptions

Signal Pin Type Description

Clock and Reset

PWG 17 I Power-Good Input. This signal comes from the power

supply to indicate that power is available and stable.

CPURST 49 O CPU Reset includes cold and warm reset 3.3V signal

(connected to CPU INIT)

RSTDRV 57 O CPU Cold Reset. 3.3V signal (connected to CPU RESET)

OSC14M 43 I 14.318Mhz Clock Input. This is used for 8254 timer clock.

PCI Interface

PCICLK 71 I PCI clock for internal PCI interface.

AD[31:0] 73-80, 83-90,

100-104, 106-

109, 111-118

I/O Address and Data are multiplexed on PCI bus. During

the first clock of a PCI transaction, AD[31-0] contains a

physical address. During subsequent clocks, AD[31-0]

contains data.

C/BEJ[3:0] 81, 91, 99,

110

I/O Bus Command and Byte Enable. During address phase,

CBEJ[3:0] define the bus command. During data phase,

CBEJ[3:0] define the byte enables.

FRAMEJ 92 I/O Cycle Frame. is driven by current initiator to indicate the

beginning and duration of an access.

DEVSELJ 95 I/O Device Select. . This indicates that the target device has

decoded the address as its own cycle. This pin is an

output pin when the M1523 acts as a PCI slave that has

decoded address as its own cycle including subtractive

decoding.

IRDYJ 93 I/O Initiator Ready indicates the initiator’s ability to complete

the current data phase of the transaction.

TRDYJ 94 I/O Target Ready indicates the target's ability to complete the

current data phase of the transaction.

STOPJ 96 I/O Stop indicates to the M1523 is requesting a master to stop

the current transaction.

PAR 98 I/O Parity Signal. PAR is even parity and is calculated on

AD[31:0] and CBEJ[3:0]. When the M1523 acts as a PCI

master, it drives PAR one PCI clock after address phase

for a read/write transaction and one PCI clock after data

phase for a write transaction. When the M1523 acts as

target, it drives PAR one PCI clock after data phase for a

PCI master read transaction.

SERRJ 97 I System Error may be pulsed active by any agent that

detects a system error condition. When SERRJ is

sampled low, the M1523 asserts NMI to send an interrupt

to the CPU.