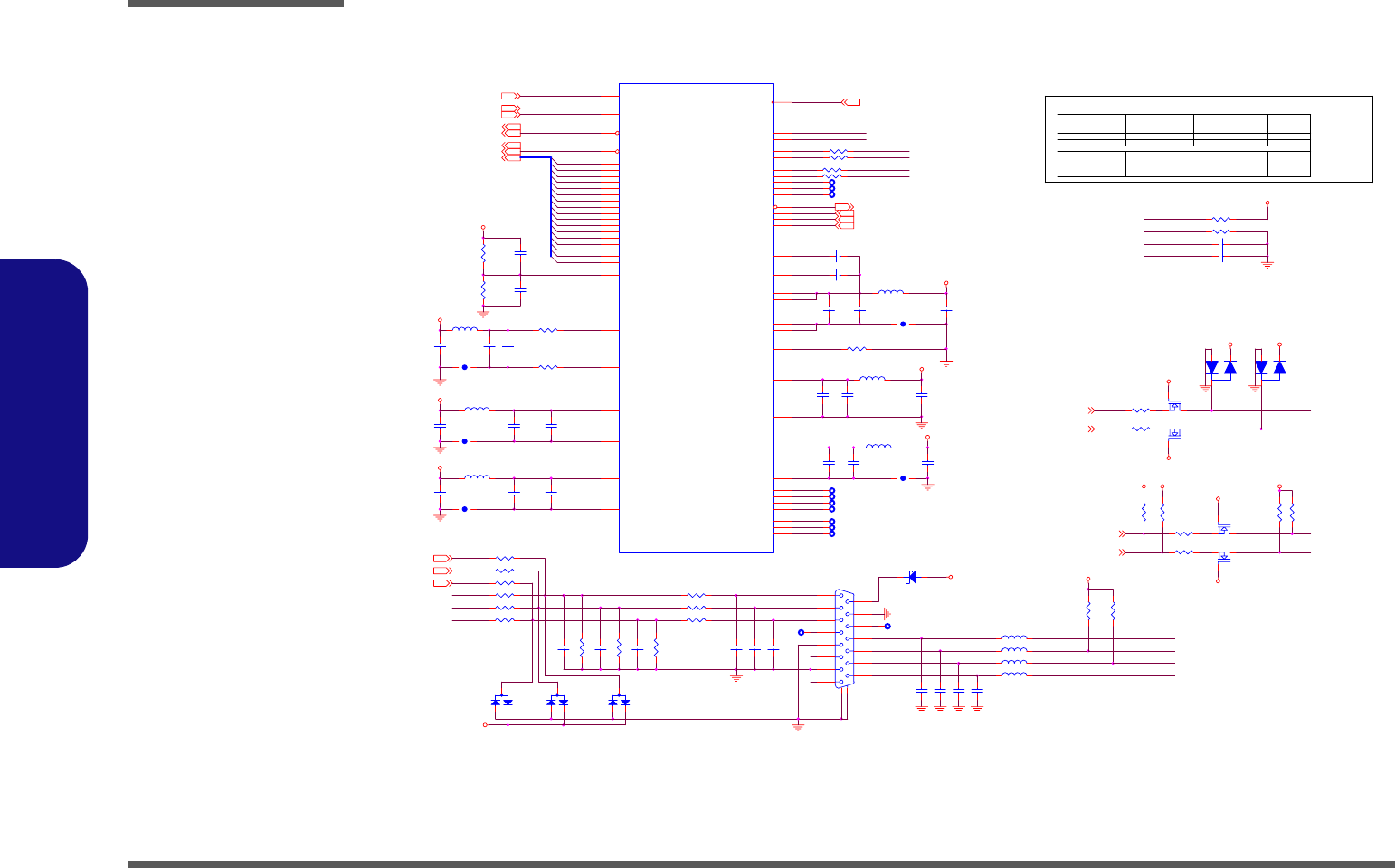

Schematic Diagrams

B - 8 M648FX-3 & CRT Out 3 of 4 (71-D40U0-D03)

B.Schematic Diagrams

M648FX-3 & CRT Out 3 of 4

+3VS

+1.8VS

+1.8VS

+3VS

+3VS

+1.8VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+5VS +5VS

+5VS

+3VS

+5VS

+5VS

ZCLK04

ZUREQ13

ZDREQ13

ZSTB013

ZSTB#013

ZSTB113

ZSTB#113

ZAD[0..16]13

VSY30

HSY30

VGADDCDATA30

VGADDCCLK30

R30

G30

B30

INTA# 10,13,30

AUXOK 15,24,27,28

PWRGD 15,29

REFCLK0 4

PCIRST# 10,13,14,20,22,24,30

Z1XAVDD

RSYNC

PWRGD

AUXOK

ENTEST

ZAD10

ZSTB0

ZAD12

ZAD6

ZSTB#0

ZAD8

ZSTB#1

ZCMP_P

ZAD15

ZCLK0

ZAD14

ZAD9

ZAD1

ZAD0

ZUREQ

ZDREQ

ZAD7

ZVREF

ZAD2

ZAD13

ZAD11

ZAD5

ZAD3

ZSTB1

ZAD4

TRAP1

TRAP0

TMODE2

TMODE1

TMODE0

DLLEN#

ENTEST

ECLKAVDD

DCLKAVDD

VVBWN

DACAVSS

VRSET

DACAVDD

VCOMP

Z1XAVSS

Z4XAVSS

Z4XAVDD

ZCMP_N

ECLKAVSS

ZAD[0..16]

MID1_10

FGRN_10

FBLU_10

DDC1CLK

VS_10

FRED_10

HSYNC

MID3_10

HS_10

DDC1DATA

B

R

G

GOUT

BOUT

ROUT

ZAD16

VSYNC

Z0802

GOUT

RSYNC

INTA#

ROUT

HSYNC

VSYNC

CSYNC

HSYNC

VSYNC

DDC1DATA

DDC1DATA

DDC1CLK

AUXOK

LSYNC

Z0801

DDC1CLK

REFCLK0

BOUT

PCIRST#

PWRGD

C6

220P

L36

FCM1608K121

1 2

R272

33

R275

33(R)

Q24

2N7002

G

S D

R277

33(R)

N3

C268

220P

C11

22P

D3

DA204U

C

A

AC

C3

22P

R447

50

Q23

2N7002

G

S D

VJVGA1

CEN/VGA DSUB

8

7

6

5

4

3

2

1

9

10

11

12

13

14

15

16

17

L10

FCM1608K121

1 2

R278

4.7K

T

C598 0.1UF

C284

22P

R5 0

L128

FCM1608K121

1 2

R258

4.7K(R)

C17

10U/10V

T

R428

56

L65

FCM1608K121

1 2

BGA1C

661

A15

C10

AH5

AK2

AJ4

AJ6

AH2

AH4

AG3

AG6

AF4

AG2

AF5

AG4

AD2

AE6

AE2

AE4

AL3

AL6

AL4

AK5

AJ2

AJ3

AE3

AF2

AK4

AD5

AD4

AN1

AM2

AL2

AL1

AN2

AM4

AN3

F9

D10

C9

B9

B10

E10

D9

B15

C15

D14

C13

D13

C12

E15

D15

E14

D12

E12

D11

B12

B13

A13

A11

B11

E13

C11

B14

C14

VOSCI

INT#A

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZCLK

ZUREQ

ZDREQ

ZSTB0

ZSTB0#

ZSTB1

ZSTB1#

ZVREF

ZCOMP_N

ZCOMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

PCIRST#

PWROK

AUXOK

TRAP1

TRAP0

TESTMODE2

TESTMODE1

TESTMODE0

DLLEN#

ENTEST

DCLKAVDD

DCLKAVSS

DACAVDD2

DACAVSS2

DACAVDD1

DACAVSS1

VCOMP

VRSET

VVBWN

CSYNC

RSYNC

LSYNC

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

ECLKAVDD

ECLKAVSS

R247 FCM1608K121

C110

0.01UF

R4 0(R)

C550

0.1UF

L31

FCM1608K121

1 2

N4

C9

22P

T

C526

0.1UF

T

R20 130_1%

T

D8

DA221(R)

3 2

1

C527

10U/10V

T

C24

0.1UF

T

R248 0

D2 F01J2E

AC

R253

75

C25

0.1UF

C10

22P

R249 0(R)

R273

4.7K

R257

2.2K

R251 0(R)

L66

FCM1608K121

1 2

T

N17

R18

2.2K

C21

1UF

T

R265

33

C267

22P

R434

56

R271

4.7K

Q22

2N7002

G

S D

C551

0.1UF

C8

220P

C305

10U/10V

C123

10U/10V

C528

0.01UF

R279 4.7K

L2

FCM1608K121

1 2

N1

C314

1UF

C26

1UF

R276 100(R)

C313

0.1UF

C22

0.1UF

C549

0.1UF

N10

C23

0.1UF

D4

DA204U

C

A

AC

R274 100(R)

C304

10U/10V

L67

FCM1608K121

1 2

R446

150

C109

0.1UF

C552

10U/10V

R250

75

R11

75

T

C95

0.01UF

R9 0

D10

DA221(R)

3 2

1

R270

33

L13

FCM1608K121

1 2

R6 FCM1608K121 R256

4.7K(R)

T

T

R3 FCM1608K121

C7

220P

D23

DA204U

C

A

AC

Q25

2N7002

G

S D

L78

FCM1608K121

1 2

C94

0.1UF

R21

33

DLLEN#

DRAM_SEL

TRAP0

TRAP1

SDR

LSYNC

CSYNC

RSYNC

1(DDR)

(30~50K Ohm)Default

DDR

0

1

0

embedded pull-low

0

0 yes

disable PLL

yes

1

NB debug mode

0

yes

0

normal

NOTE: This page is for universal PCB design( suitable for both 645 or 650)

NB Hardware Trap Table

enable panel link

enable VGA interface

enable PLL

TV selection, NTSC/PAL(0/1)

enable VB

35.4mA

6.49mA

7.92mA

84.8mA

7.57mA

18.07mA

20MIL

10MIL

10MIL

10MIL

20MIL

10MIL

Sheet 7 of 42

M648FX-3

& CRT Out

3 of 4