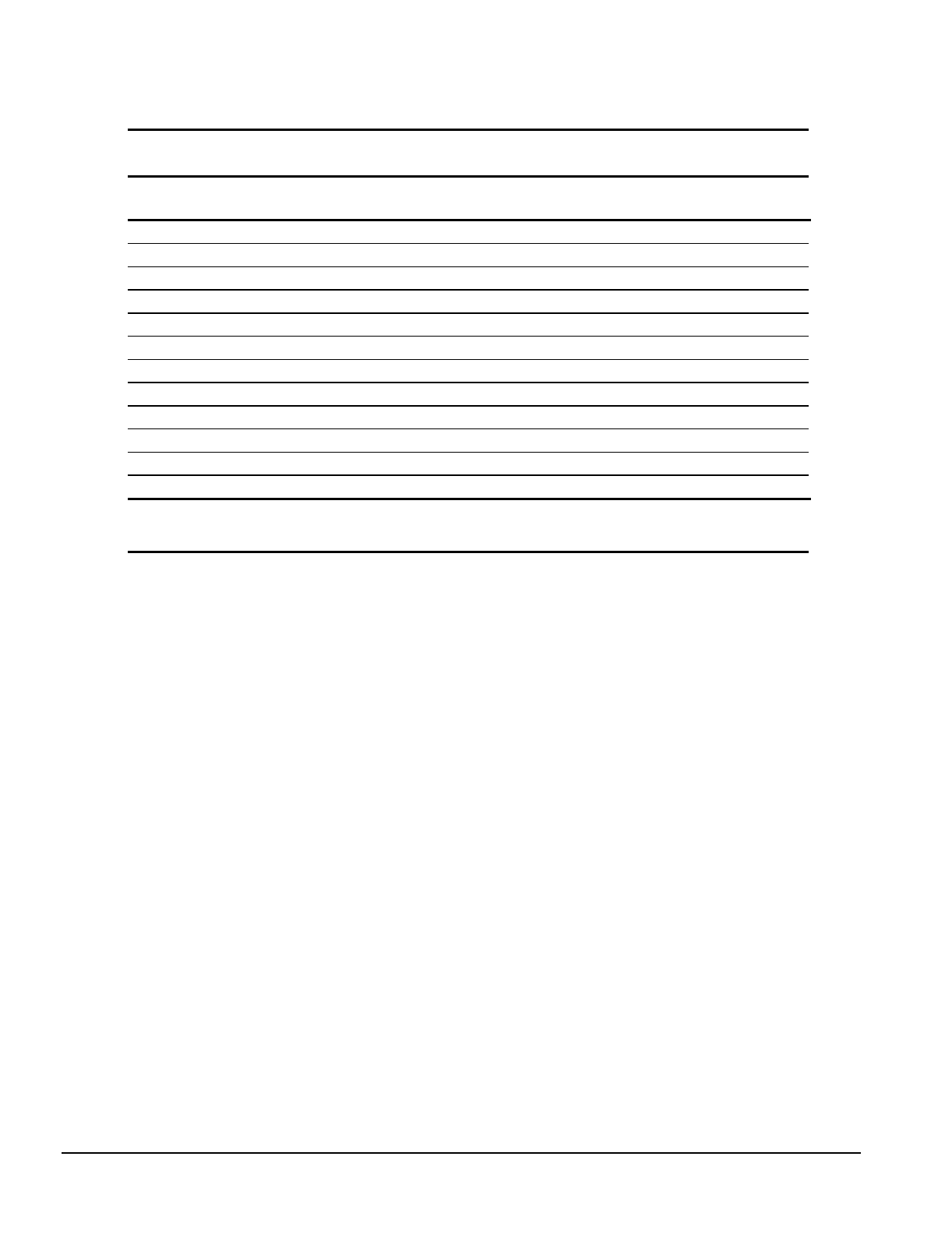

H-2 Intel 44LX Chipset Memory Limitations

Table H-1

SDRAM Memory Technologies

SDRAM

Size

Address

Locations

SDRAM

Width

Number Of Chips Non-ECC

(64 bits)

Number Of Chips ECC

(72 bits)

DIMM

Size

1M×16 1M ×16 4 chips total, 1 side 5 or 6 chips total -1 side 8 MB

1M×16 1M ×16 8 chips total, 4 per side 10 or 12 chips total, 5 or 6 per side 16 MB

2M×8 2M ×8 8 chips total , 1 side 9 chips total , 1 side 16 MB

2M×8 2M ×8 16 chips total, 8 per side 18 chips total, 9 per side 32 MB

4M×4 4M ×4 16 chips total , 1 side 18 chips total, 1 side 32 MB

4M×4 4M ×4 32 chips total, 16 per side 36 chips total, 18 per side 64 MB

4M×16 4M ×16 4 chips total, 1 side 5 or 6 chips total, 1 side 32 MB

4M×16 4M ×16 8 chips total, 4 per side 10 or 12 chips total, 5 or 6 per side 64 MB

8M×8 8M ×8 8 chips total , 1 side 9 chips total , 1 side 64 MB

8M×8 8M ×8 16 chips total, 8 per side 18 chips total, 9 per side 128 MB

16M×4 16M ×4 16 chips total , 1 side 18 chips total, 1 side 128 MB

16M×4 16M ×4 32 chips total, 16 per side 36 chips total, 18 per side 256 MB

Note:

This information is intended to be used as a guide to identifying the memory technology used for SDRAM DIMMs and

may not include all technologies. Some of the configurations may not exist in the marketplace.

For example, a 32-MB DIMM with 8 chips per side for 16 chips total is most likely comprised of

16 Mb (2M×8) technology SDRAMs giving a data width of ×8.

That same 32-MB DIMM with only 4 chips on one side is most likely comprised of 64 Mb (4M×16)

technology SDRAMs with a data width of ×16.