4–80 Alpha Architecture Handbook

VAX and IEEE subsets, appropriately set the FPCR exception bits. It is UNPREDICTABLE

whether floating-point operates that belong only to the VAX floating-point subset set the

FPCR exception bits.

Alpha floating-point hardware only transitions these exception bits from zero to one. Once set

to one, these exception bits are only cleared when software writes zero into these bits by writ-

ing a new value into the FPCR.

Section 4.7.2 allows certain of the FPCR bits to be subsetted.

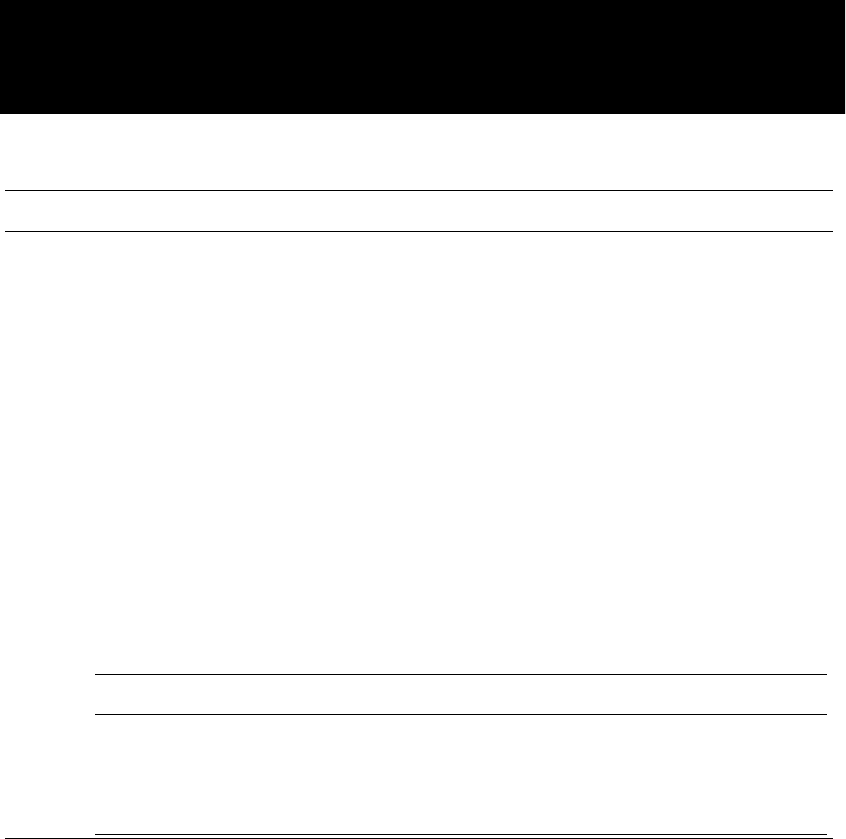

The format of the FPCR is shown in Figure 4–1 and described in Table 4–11.

Figure 4–1: Floating-Point Control Register (FPCR) Format

Table 4–11: Floating-Point Control Register (FPCR) Bit Descriptions

Bit Description (Meaning When Set)

63 Summary Bit (SUM). Records bitwise OR of FPCR exception bits. Equal to

FPCR<57 |56 | 55 | 54 | 53 | 52>.

62

Inexact Disable (INED)

†

. Suppress INE trap and place correct IEEE nontrapping

result in the destination register.

61

Underflow Disable (UNFD)

†

. Suppress UNF trap and place correct IEEE nontrap-

ping result in the destination register if the implementation is capable of produc-

ing correct IEEE nontrapping result. The correct result value is determined

according to the value of the UNDZ bit.

60

Underflow to Zero (UNDZ)

†

. When set together with UNFD, on underflow, the

hardware places a true zero (64 bits of zero) in the destination register rather than

the result specified by the IEEE standard.

59–58 Dynamic Rounding Mode (DYN). Indicates the rounding mode to be used by an

IEEE floating-point operate instruction when the instruction’s function field spec-

ifies dynamic mode (/D). Assignments are:

63 62 60

0

S

U

M

O

V

N

E

U

N

F

O

V

F

D

Z

E

N

V

5859 5756 5554 5352 51

RAZ/IGN

N

V

504948

D

D

Z

E

D

O

V

F

D

DYN

_RM

U

N

D

Z

U

N

F

61

D

N

E

D

II I

II

4746

D

N

Z

N

O

D

D

DYN IEEE Rounding Mode Selected

00 Chopped rounding mode

01 Minus infinity

10 Normal rounding

11 Plus infinity