ICE CONTROL SOFTWARE ICS62XX

VIII-14 EPSON S1C62 FAMILY

DEVELOPMENT TOOL REFERENCE MANUAL

2.3.6 Target interrupt and break

When a target interrupt occurs the moment of a break it is given priority over the break. The break is then

induced after the interrupt process is stacked. Next, the interrupt routine is executed from the top when the

run mode commences.

The PC displayed during a break is the top interrupt address.

When a break is set by the BR command with FI=1, the break and interrupt are generated simultaneously,

but due to the interrupt process, the register values after the break are:

*PC=0000 A=.... F=.DZC X=000 Y=010

|

FI reset

so as to reset the FI flag status.

2.3.7

History function

The evaluation board CPU information (PC, instruction code, RAM data address and data content, and

CPU internal registers) while running an emulation are fetched to the history memory region with each

CPU bus cycle. The history memory has a capacity of 8291 cycles, and can store 2730 (5 clock instructions

only) to 1365 (12 clock instructions only) new instructions executed by the evaluation board.

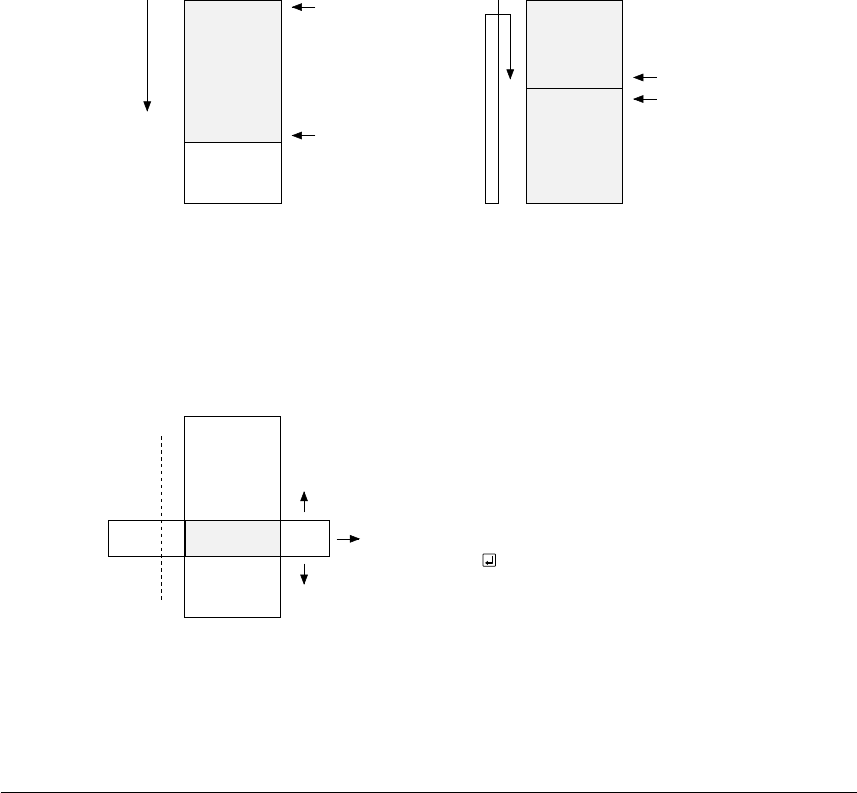

Fig. 2.3.7.2 History data display

Fig. 2.3.7.1 History function diagram

Figure 2.3.7.1 shows a diagram of the history function. When the history memory is filled, old data is

overwritten by new data.

The history pointer (HP) normally displays the oldest instruction at position 0, but during a break it

displays the newest instruction. The maximum value of the HP is about 2730 when 5 clock instructions are

executed.

Space

History memory

Effective

history

Program

execution

Oldest instruction

(HP=0)

Instruction

immediately

prior to break

(HP=700)

History memory

Effective

history

Oldest instruction

(HP=0)

(HP=2730)

Instruction

immediately

prior to break

Effective

history

Newest

instruction

History data

Oldest

instruction

HP=0

The HP can display optional positions via the H, HB,

and HG commands.

HP data from 1980 to 1986 is displayed by entering:

#H, 1980, 1986

HP=2700