S1C88650 TECHNICAL MANUAL EPSON 107

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Programmable Timer)

FTCx is the interrupt factor flag corresponding to

interrupt of Timer x, and is set to "1" with the

compare match signal.

At this point, if the corresponding interrupt enable

register is set to "1" and the corresponding inter-

rupt priority register is set to a higher level than

the setting of the interrupt flags (I0 and I1), an

interrupt is generated to the CPU.

Regardless of the interrupt enable register and

interrupt priority register settings, the interrupt

factor flag is set to "1" when the interrupt genera-

tion condition is met.

To accept the subsequent interrupt after an

interrupt generation, it is necessary to re-set the

interrupt flags (set the interrupt flag to a lower

level than the level indicated by the interrupt

priority registers, or execute the RETE instruction)

and to reset the interrupt factor flag. The interrupt

factor flag is reset to "0" by writing "1".

In the 16-bit mode, the interrupt factor flag FTC(L)

is not set to "1" and Timer(L) interrupt is not

generated. In this mode, the interrupt factor flag

FTC(H) is set to "1" by the compare match of the

16-bit counter.

At initial reset, this flag is reset to "0".

5.10.10 Programming notes

(1) The programmable timer actually enters into

RUN or STOP status at the falling edge of the

input clock after writing to the PTRUNx

register. Consequently, when "0" is written to

PTRUNx, the timer stops after counting once

more (+1). PTRUNx is read as "1" until the

timer actually stops.

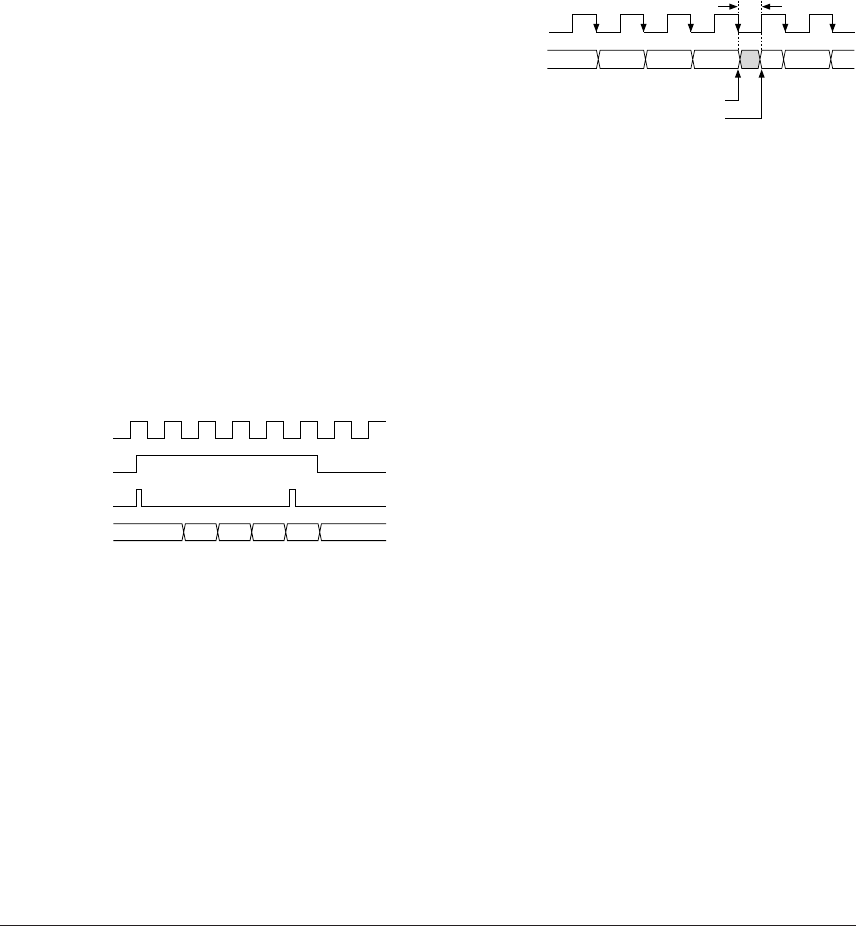

Figure 5.10.10.1 shows the timing chart at the

RUN/STOP control.

PTRUNx(WR)

PTMx 42H 41H 40H 3FH 3EH 3DH

PTRUNx(RD)

Input clock

Fig. 5.10.10.1 Timing chart at RUN/STOP control

(2) When the SLP instruction is executed while the

programmable timer is running (PTRUNx =

"1"), the timer stops counting during SLEEP

status. When SLEEP status is canceled, the

timer starts counting. However, the operation

becomes unstable immediately after SLEEP

status is canceled. Therefore, when shifting to

SLEEP status, stop the 16-bit programmable

timer (PTRUNx = "0") prior to executing the

SLP instruction.

Same as above, the TOUT signal output should

be disabled (PTOUTx = "0") so that an unstable

clock is not output to the clock output port

terminal.

(3) In the 16-bit mode, reading PTM(L) does not

latch the Timer(H) counter data in PTM(H). To

avoid generating a borrow from Timer(L) to

Timer(H), read the counter data after stopping

the timer by writing "0" to PTRUN(L).

(4) For the reason below, pay attention to the

reload data write timing when changing the

interval of the programmable timer interrupts

while the programmable timer is running.

The programmable timer counts down at the

falling edge of the input clock and at the same

time it generates an interrupt if the counter

underflows. Then it starts loading the reload

data to the counter and the counter data is

determined at the next rising edge of the input

clock (period shown in as ➀ in the figure).

Input clock

Counter data

(continuous mode)

(Reload data = 25H)

03H 02H 01H 00H 25H 24H

Underflow (interrupt is generated)

Counter data is determined by reloading

➀

Fig. 5.10.10.2 Reload timing for programmable timer

To avoid improper reloading, do not rewrite

the reload data after an interrupt occurs until

the counter data is determined including the

reloading period ➀. Be especially careful when

using the OSC1 (low-speed clock) as the clock

source of the programmable timer and the CPU

is operating with the OSC3 (high-speed clock).