14 EPSON S1C88650 TECHNICAL MANUAL

3 CPU AND BUS CONFIGURATION

3.6.6 Bus authority release state

The S1C88650 is equipped with a bus authority

release function on request from an external device

so that DMA (Direct Memory Access) transfer can

be conducted between external devices. The

internal memory cannot be accessed by this

function.

There are two terminals used for this function: the

________

bus authority release request signal (BREQ) input

terminal and the bus authority release acknowledge

________

signal (BACK) output terminal.

________

The BREQ input terminal is shared with input port

________

terminal K03 and the BACK output terminal with

output port terminal R33, use with setting to

________ ________

BREQ/BACK terminals done in software. In the

single chip mode, or when using a system which

does not require bus authority release, set respec-

tive terminals as input and output ports.

Input

port

K03

Output

port

R33

BREQ

input

BACK

output

_______

_______

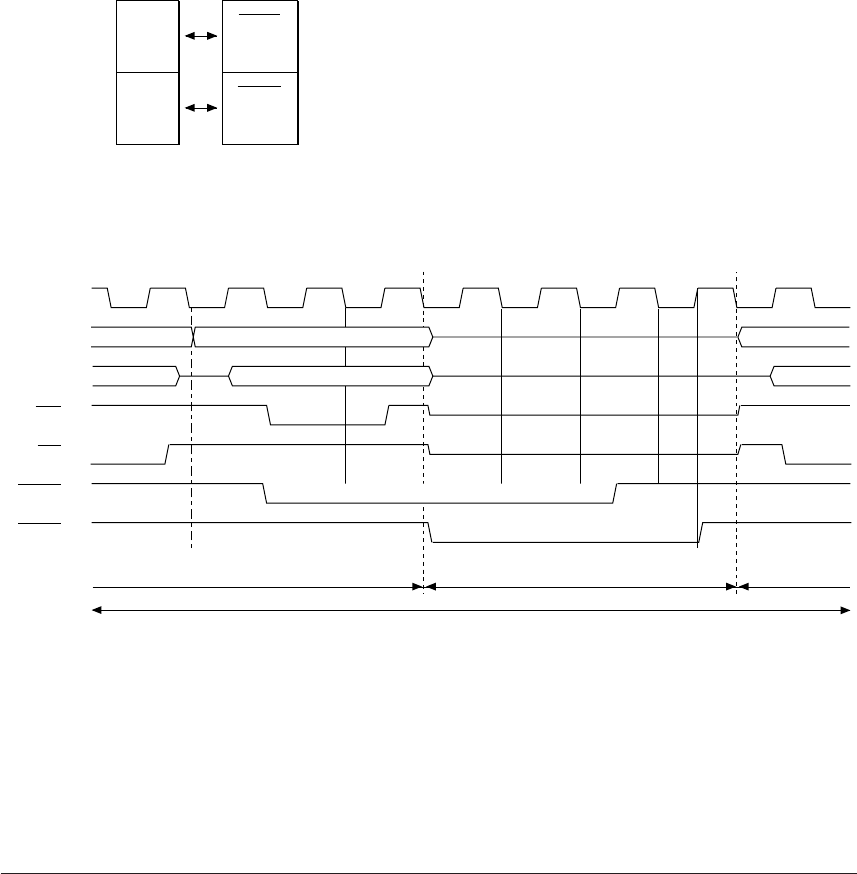

Fig. 3.6.6.1 BREQ/BACK terminals

________

When the bus authority release request (BREQ =

LOW) is received from an external device, the

____

S1C88650 switches the address bus, data bus, RD/

_____ ____

WR signal, and CE signal lines to a high impedance

________

state, outputs a LOW level from the BACK terminal

and releases bus authority.

________

As soon as a LOW level is output from the BACK

terminal, the external device can use the external

bus. When DMA is completed, the external device

________

returns the BREQ terminal to HIGH and releases

bus authority.

Figure 3.6.6.2 shows the bus authority release

sequence.

During bus authority release state, internal memory

cannot be accessed from the external device. In

cases where external memory has areas which

overlap areas in internal memory, the external

memory areas can be accessed accordance with the

____

CE signal output by the external device.

Note: Be careful with the system, such that an

external device does not become the bus

master, other than during the bus release

status.

_______

After setting the BREQ terminal to LOW

_______

level, hold the BREQ terminal at LOW level

_______

until the BACK terminal becomes LOW level.

_______

If the BREQ terminal is returned to HIGH

_______

level, before the BACK terminal becomes

LOW level, the shift to the bus authorization

release status will become indefinite.

CLK

A0–A19

D0–D7

WR

RD

BREQ

BACK

Program exection status

LD [HL],[IX]

PCHL

ANY

(IX)

Tw2 T4 T1 T2 T3 Tw1 Tw2 T4 Tz1 Tz2 Tz1 Tz2 Tz1 Tz2 Tz1 Tz2 T1 T2 T3

IX

(IX)

Bus authority release status

Program

exection

status

LLLLH

Fig. 3.6.6.2 Bus authority release sequence