36 EPSON S1C88650 TECHNICAL MANUAL

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (System Controller and Bus Control)

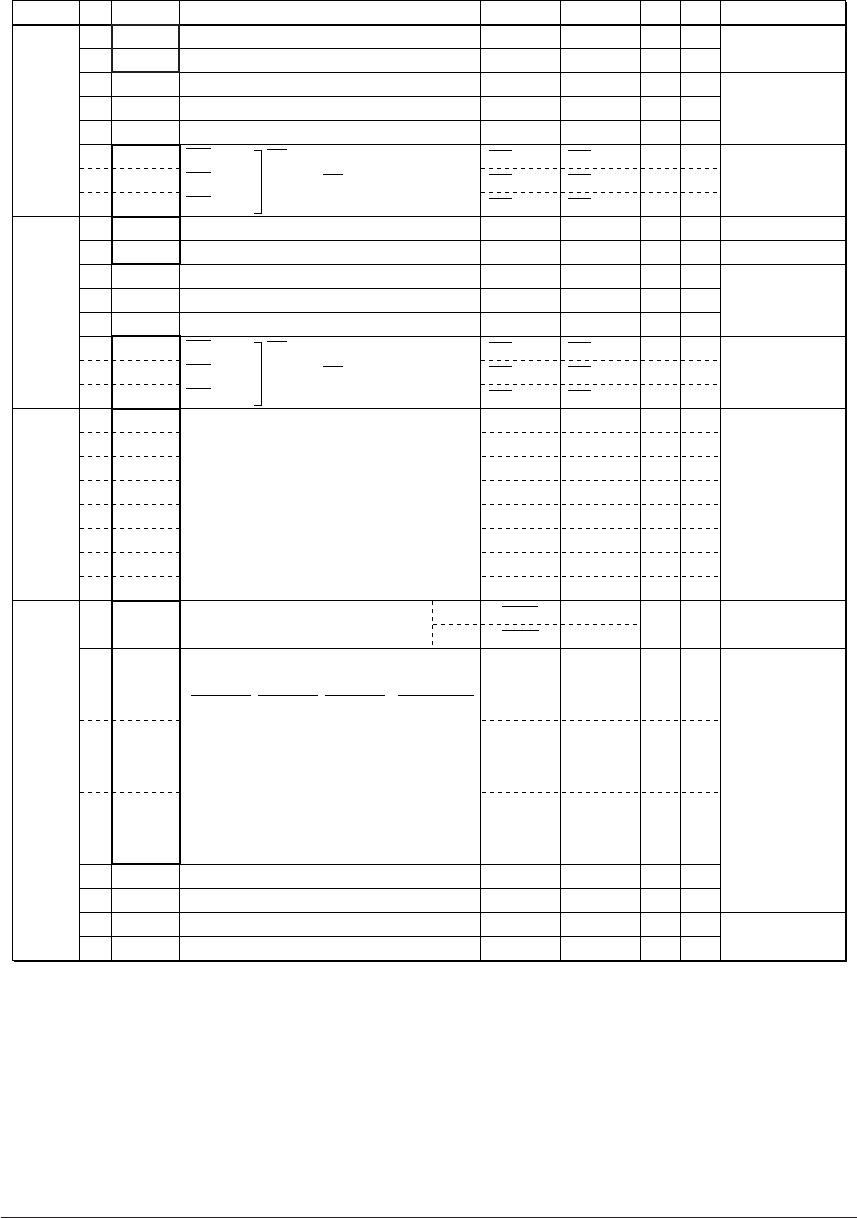

5.2.6 Control of system controller

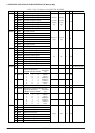

Table 5.2.6.1 shows the control bits for the system controller.

Table 5.2.6.1 System controller control bits

SR R/W10Address Bit Name Function Comment

00FF00

(MCU)

D7

D6

D5

D4

D3

D2

D1

D0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bus mode

CPU mode

R/W register

R/W register

R/W register

CE2 (R32)

CE1 (R31)

CE0 (R30)

Reserved register

In Single chip mode,

these setting are fixed

at DC output.

CE signal output

DC (R3x) output

Expansion

Maximum

1

1

1

CE2 enable

CE1 enable

CE0 enable

Single chip

Minimum

0

0

0

CE2 disable

CE1 disable

CE0 disable

BUSMOD

CPUMOD

–

–

–

CE2

CE1

CE0

CE signal output Enable/Disable

Enable:

Disable:

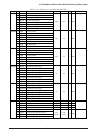

00FF00

(MPU)

D7

D6

D5

D4

D3

D2

D1

D0

1

0

0

0

0

0

0

1

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bus mode

CPU mode

R/W register

R/W register

R/W register

CE2 (R32)

CE1 (R31)

CE0 (R30)

Expansion mode only

Reserved register

Expansion

Maximum

1

1

1

CE2 enable

CE1 enable

CE0 enable

–

Minimum

0

0

0

CE2 disable

CE1 disable

CE0 disable

BUSMOD

CPUMOD

–

–

–

CE2

CE1

CE0

CE signal output Enable/Disable

Enable:

Disable:

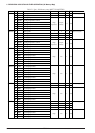

00FF01 D7

D6

D5

D4

D3

D2

D1

D0

SPP7

SPP6

SPP5

SPP4

SPP3

SPP2

SPP1

SPP0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

0

Stack pointer page address

< SP page allocatable address >

• Single chip mode:

• Expansion mode:

1

1

1

1

1

1

1

1

(MSB)

(LSB)

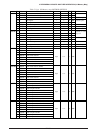

00FF02 D7

D6

D5

D4

D3

D2

D1

D0

EBR

WT2

WT1

WT0

CLKCHG

SOSC3

–

–

0

0

0

0

1

1

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

BREQ

BACK

OSC3

On

1

1

WT2

1

1

1

1

0

0

0

0

WT1

1

1

0

0

1

1

0

0

WT0

1

0

1

0

1

0

1

0

Number

of state

14

12

10

8

6

4

2

Input port

Output port

OSC1

Off

0

0

Bus release enable register

(K03 and R33 terminal specification)

Wait control register

CPU operating clock switch

OSC3 oscillation On/Off control

R/W register

R/W register

No wait

Reserved register

K03

R33

only 0 page

0–27H page

CE signal output

DC (R3x) output

Note:

____

All the interrupts including NMI are disabled, until you write the optional value into both the "00FF00H" and

"00FF01H" addresses.