66 EPSON S1C88650 TECHNICAL MANUAL

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Serial Interface)

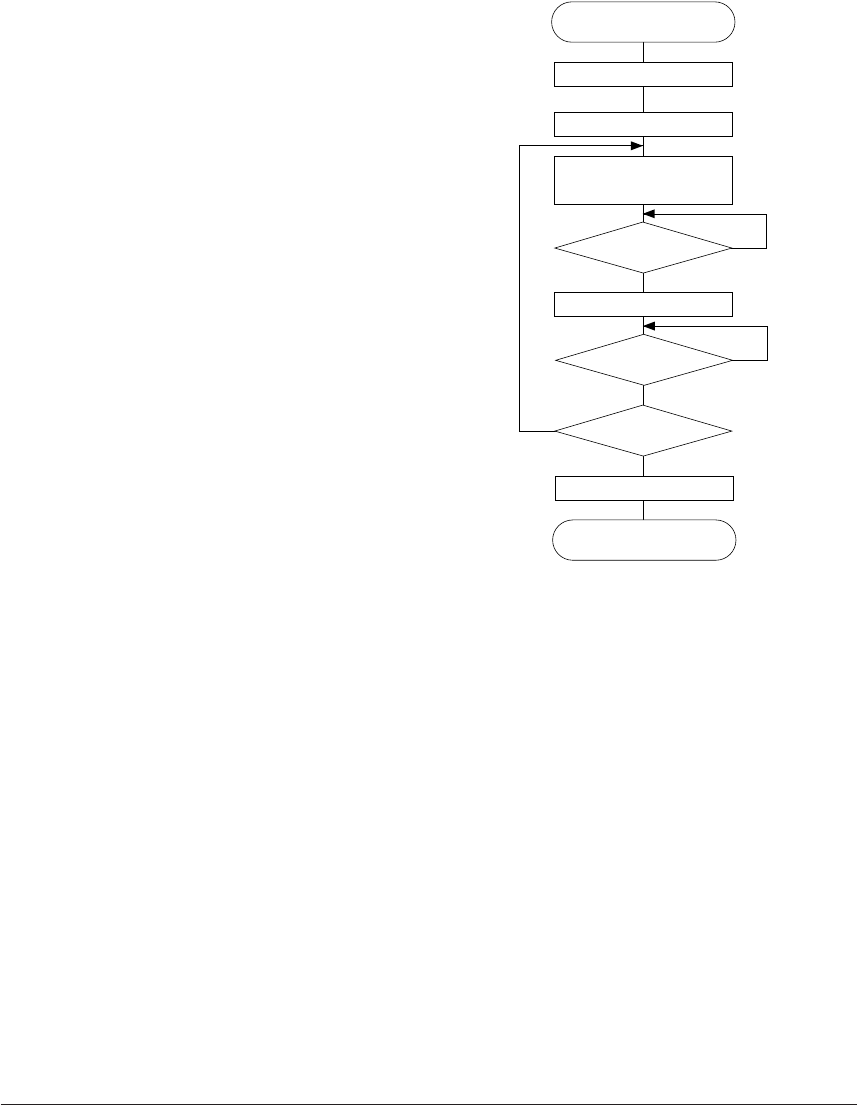

■ Data transmit procedure

The control procedure and operation during

transmitting is as follows.

(1) Write "0" in the transmit enable register TXEN

and the receive enable register RXEN to reset

the serial interface.

(2) Write "1" in the transmit enable register TXEN

to set into the transmitting enable status.

(3) Write the transmitting data into TRXD0–

TRXD7.

(4) In case of the master mode, confirm the receive

ready status on the slave side (external serial

input/output device), if necessary. Wait until it

reaches the receive ready status.

(5) Write "1" in the transmit control bit TXTRG and

start transmitting.

In the master mode, this control causes the

synchronous clock to change to enable and to be

provided to the shift register for transmitting

_________

and output from the SCLK terminal.

In the slave mode, it waits for the synchronous

_________

clock to be input from the SCLK terminal.

The transmitting data of the shift register shifts

one bit at a time at each falling edge of the

synchronous clock and is output from the SOUT

terminal. When the final bit (MSB when "LSB

first" is selected, or LSB when "MSB first" is

selected) is output, the SOUTx terminal is

maintained at that level, until the next

transmitting begins.

The transmitting complete interrupt factor flag

FSTRA is set to "1" at the point where the data

transmitting of the shift register is completed.

When interrupt has been enabled, a transmit-

ting complete interrupt is generated at this

point.

Set the following transmitting data using this

interrupt.

(6) Repeat steps (3) to (5) for the number of bytes of

transmitting data, and then set the transmit

disable status by writing "0" to the transmit

enable register TXEN, when the transmitting is

completed.

Data transmitting

End

TXEN ← 0, RXEN ← 0

No

Yes

Transmit complete ?

Set transmitting data

to TRXD0–TRXD7

No

Yes

FSTRA = 1 ?

TXEN ← 0

TXTRG ← 1

TXEN ← 1

No

Yes

Receiver ready ?

In case of master mode

Fig. 5.8.6.2 Transmit procedure in clock synchronous mode