18 BladeSymphony 1000 Architecture White Paper www.hitachi.com

L3 Cache Copy Tag

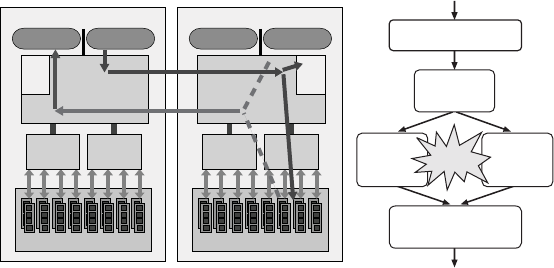

The data residing in caches and main memory across Intel Itanium Server Blades are kept in sync by

using a snooping cache coherency protocol. When one of the Intel Itanium processors needs to access

memory, the requested address is broadcast by the Hitachi Node Controller. The other Node

Controllers that are part of that partition (SMP) listen for (snoop) those broadcasts. The Node Controller

keeps track of the memory addresses currently cached in each processor’s on-chip caches by

assigning a tag for each cache entry. If one of the processors contains the requested data in its cache it

initiates a cache-to-cache transfer. This reduces latency by avoiding the penalty to retrieve data from

main memory and helps maintain consistency by sending the requesting processor the most current

data. In order to save bandwidth on the processors’ front side bus, the Node Controller is able to use

the L3 Cache Copy Tags to determine which memory address broadcasts its two local processors

need to see. If a requested address is not in the processors’ cache, the Node Controller filters the

request and does not forward the request to the local processors. This process is illustrated in

Figure 10.

Figure 10. L3 cache copy tag process

Intel Itanium I/O Expansion Module

Some applications require more PCI slots than the two that are available per server blade. The Intel

Itanium I/O Expansion Module provides more ports, without the expense of additional server blades.

Using the Itanium I/O Expansion Module with the Intel Itanium Server Blade can increase the number of

the PCI expansion-card slots that can be connected to the Intel Itanium Server Blade. The Itanium I/O

expansion module cannot be used in with the Intel Xeon Server Blade.

The Intel Itanium I/O Expansion Module increases the number of PCI I/O slots to either four or eight

slots depending on the chassis type. The type A chassis enables connection to four PCI I/O slots

(Figure 11), and the type B chassis enables up to eight PCI I/O slots (Figure 12).

Main Memory

Node 0

Node

Controller

L3 C

Copy

Tag

Itanium2 Itanium2

Main Memory

Node 1

Node

Controller

L3 C

Copy

Tag

Itanium2 Itanium2

Memory

Controller

Memory

Controller

Memory

Controller

Memory

Controller

(1)

(2)

(4)

(3)’

(3)

(4) Memory data transfer

or

Cache data transfer

(3)

Memory

access

(3)’ Cache

consistency

control over

remote nodes

(2) Memory

address

broadcasting

(1) Cache consistency

control within a local node

Parallel

Processing