www.hitachi.com BladeSymphony 1000 Architecture White Paper 23

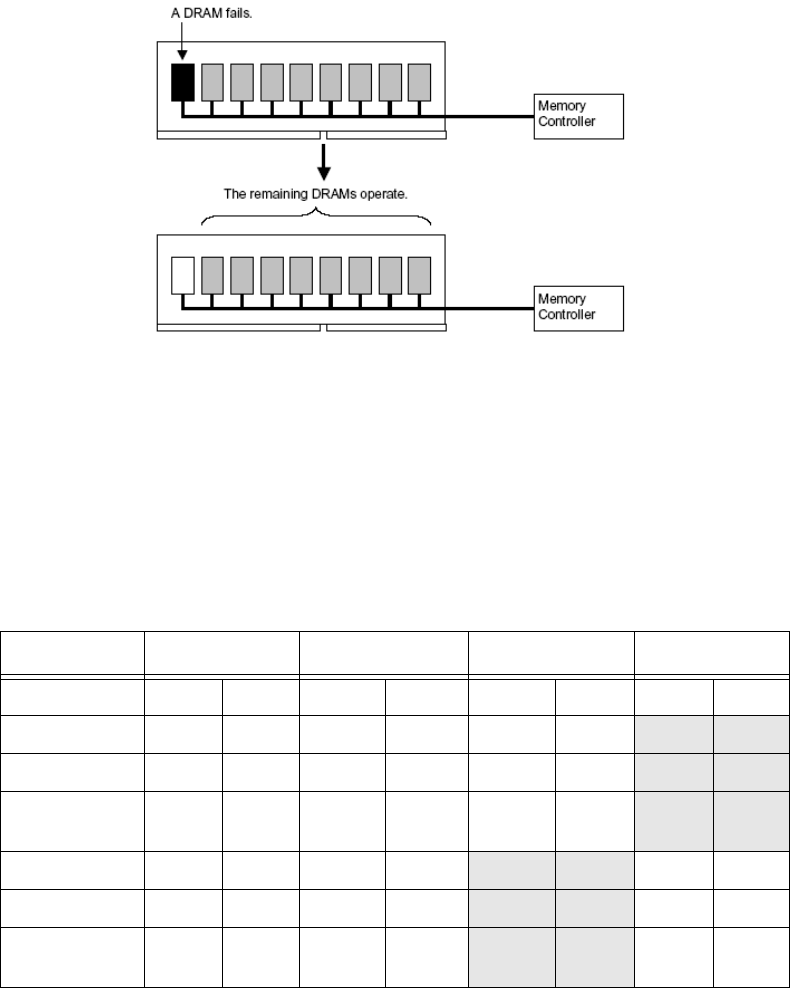

Advanced ECC

Conventional ECC is intended to correct 1-bit errors and detect 2-bit errors. Advanced ECC, also

known as Chipkill, corrects up to four or eight bits of an error that occurs in a DRAM installed on a

x4- DRAM or x8-DRAM type DIMM, respectively. Accordingly, the system can operate normally even if

one DRAM fails, as illustrated in Figure 14.

Figure 14. Advanced ECC

Online Spare Memory

Online spare memory provides the functionality to switch over to spare memory if correctable errors

frequently occur. This function is enabled to prevent system downtime caused by a memory fault.

BladeSymphony 1000 supports the online spare memory function in the ten patterns of memory

configurations listed in Table 5. The shaded sections represent spare banks. Online spare memory

excludes the use of the memory mirroring function.

Table 5: Online spare memory supported configurations

Bank Bank1 Bank2 Bank3 Bank4

Slot Slot 1 Slot 2 Slot 3 Slot 4 Slot 5 Slot 6 Slot 7 Slot 8

Configuration 1 2 GB 2 GB 2 GB 2 GB 2 GB 2 GB

2 GB 2 GB

Configuration 2 1 GB 1 GB 1 GB 1 GB 1 GB 1 GB

1 GB 1 GB

Configuration 3 512

MB

512

MB

512 MB 512

MB

512 MB 512

MB

512

MB

512

MB

Configuration 4 2 GB 2 GB 2 GB 2 GB

2 GB 2 GB None None

Configuration 5 1 GB 1 GB 1 GB 1 GB

1 GB 1 GB None None

Configuration 6 512

MB

512

MB

512 MB 512

MB

512 MB 512

MB

None None