IBM RS/6000 7025 Model F80 Server 7

• 128 KB on-chip L1 instruction cache with parity and refetch

• 128 KB on-chip L1 data cache with ECC

• On-chip L2 cache directory

• 4 MB of off-chip L2 cache using ECC double data rate (DDR) SRAM per

processor for 2-, 4-, and 6-way SMPs and 2 MB of off-chip L2 cache using

ECC Single Data Rate (SDR) SRAM for a 1-way system.

• PowerPC 6xx bus architecture, 16-byte wide bus interface

The RS64 III processor is available in two operating frequencies, 450 MHz and

500 MHz. The frequency is accomplished by leveraging IBMs copper technology

(CMOS 7S) along with an innovative design of timing-critical paths.

The copper technology and an improved manufacturing process allow the chip to

operate at 1.8V. The lower operating voltage coupled with the smaller circuit

dimensions result in reduced wattage in the RS64 III and allow additional function

to be placed on the chip.

The size of the level one (L1) instruction and data caches is 128 KB each.

Innovative custom circuit design techniques were used to maintain the one cycle

load-to-use latency for the L1 data cache. The level two (L2) cache directory was

integrated into the RS64 III chip, reducing off-chip accesses which impact

performance.

IBM used double data rate (DDR) SRAM technology for the L2 cache in the RS64

III processor. DDR technology provides two transfers of data on the 16-byte wide

L2 data bus every SRAM clock cycle. The DDR SRAM technology also reduced

L2 access latency as measured by nanoseconds.

Processor Boards

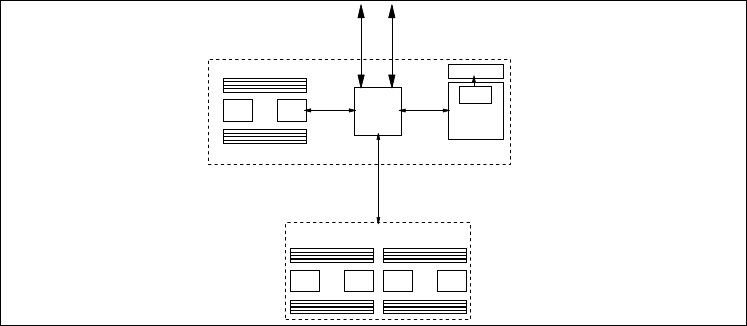

The processor boards used in the Model F80 for 1-, 2-, 4-, and 6-way SMP

configurations come in the form of a single book and are described as follows:

Single Processor

As shown in Figure 6, a single processor board consists of a single

RS64 III processor operating at 450 MHz, on-board memory slots, and

a memory controller in a single book. Upgrades to additional

processors require changing of the processor book. However, the

single processor board is a cost-reduced package.

Figure 6. RS/6000 Model F80 System Schematic for 1-Way Processor

SMI SMI

Memory Card 1

SMI SMI SMI SMI

Proc.

1 Way

2 MB Cache

6XX

Bus 0

Memory

Controller

SMI

Bus 6,7

1-Way

Mother Board

RIO

Port 0

RIO

Port 1

SMI

Bus 0,1,2,3