Optimized for virtualization and database applications with maximum

memory and compute capacity in a blade

Please see the Legal Information section for important notices and information.

7.

Intel’s Virtualization Technology (VT) integrates hardware-level virtualization hooks that allow

operating system vendors to better utilize the hardware for virtualization workloads.

DDR3 Registered Memory with Active Memory Protection

The HX5 uses registered double data rate III (DDR3) VLP (very-low-profile) DIMMs and provides

Active Memory features, including advanced Chipkill memory protection, for up to 16X better

error correction than standard ECC memory. In addition to offering triple the memory

bandwidth of DDR2 or fully-buffered memory, DDR3 memory also uses less energy. DDR2

memory already offered up to 37% lower energy use than fully buffered memory. Now, a

generation later, DDR3 memory is even more efficient, using 10-15% less energy than DDR2

memory.

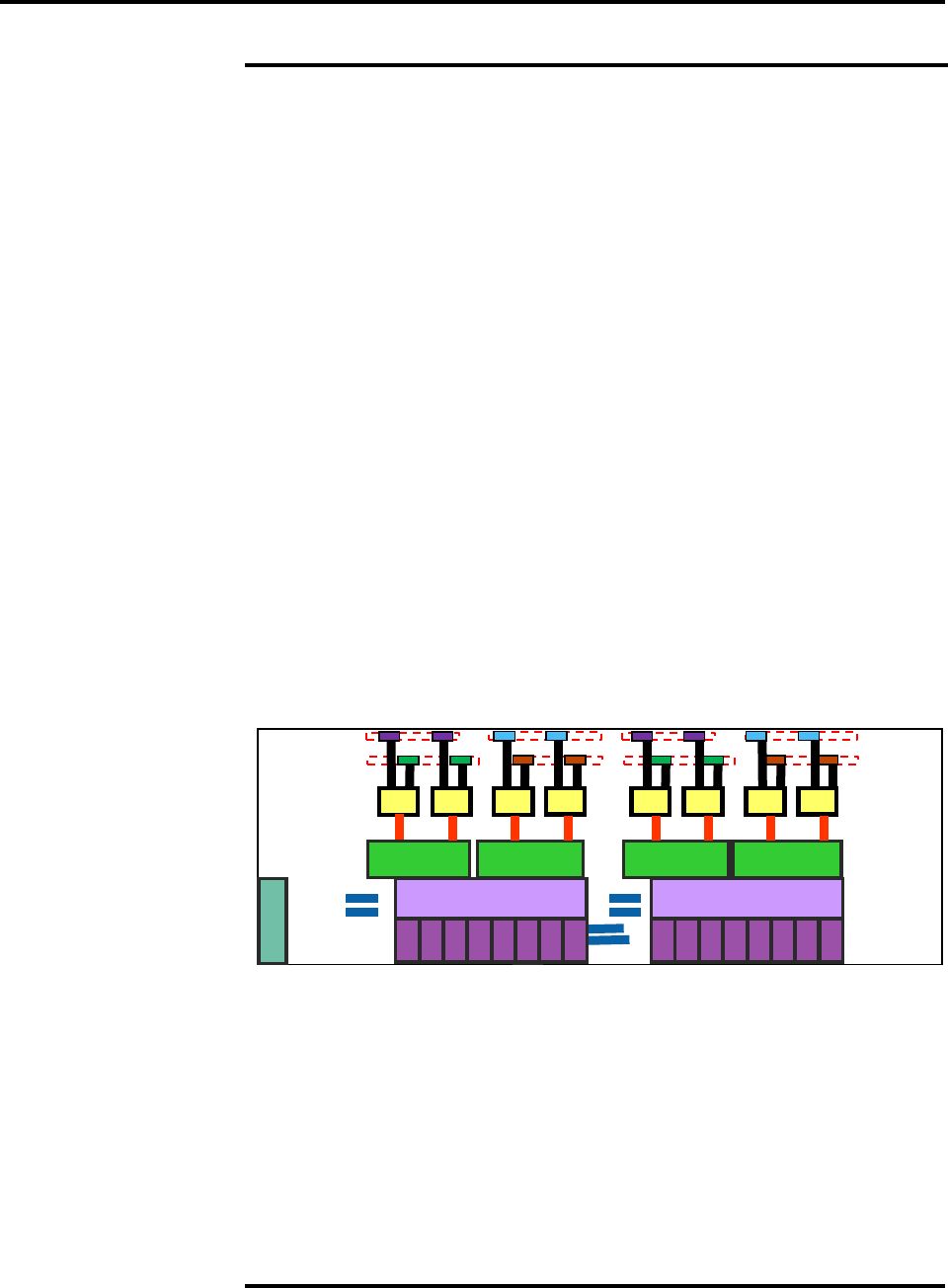

The HX5 supports up to 128GB of memory in 16 DIMM slots. Redesign in the architecture of the

Xeon 7500 series processors bring radical changes in the way memory works in these servers.

For example, the 7500 series processors integrate 2 memory controllers inside each

processor, resulting in four memory controllers in a two-socket system. Each memory controller

has four memory channels, one per pair of DIMMs. Depending on the type of memory,

population of memory, and processor model, the memory may be clocked at 978MHz or

800MHz.

Redesign in the architecture of the x7500 series processors bring radical changes in the way

memory works in these servers. For example, the Xeon 7500 series processors integrate two

memory controllers inside each processor, resulting in four memory controllers in a two-

socket system. Each processor has four memory channels.

Note: If only one processor is installed, only eight DIMM slots (up to 64GB) can be used. There

are two ways to expand memory beyond 8 DIMMs. Adding a second processor not only doubles

the amount of memory available for use, but also doubles the number of memory controllers,

thus doubling the system memory bandwidth. If you add a second processor, but no additional

memory for the second processor, the second processor has to access the memory from the first

processor “remotely,” resulting in longer latencies and lower performance. The latency to access

remote memory is almost 75% higher than local memory access. So, the goal should be to

always populate both processors with memory.

Alternatively, you can add a MAX5 memory expansion blade, containing 24 more DIMM slots

with up to 192GB of memory. This offers up to 32 DIMMs and 256GB of memory with only a

single processor. Adding the second processor allows the use of 8 more DIMM slots inside the

HX5 and a grand total of 40 DIMMs and 320GB of memory in a double-wide (60mm) blade

server. Expanding further, 2 HX5 server blades and 2 MAX5 memory blades can create one 4-

socket, 640GB powerhouse in a 4-wide blade server.

Notes: DIMMs must be installed in matching pairs. Also, each CPU requires at least 2 DIMMs. It

is important to ensure that all memory channels in each processor are populated. The relative

memory bandwidth decreases as the number of channels populated decreases. This is because

the bandwidth of all the memory channels is utilized to support the capability of the processor.

So, as the channels are decreased, the burden to support the requisite bandwidth is increased

on the remaining channels, causing them to become a bottleneck.

For peak performance:

• Always populate processors with equal amounts of memory to enable a balanced NUMA system

• Always populate both memory channels on each processor with equal memory capacity

• Ensure an even number of ranks are populated per channel

Power guidelines:

• Fewer larger DIMMs (for example 8 x 4GB DIMMs vs. 16 x 2GB DIMMs will generally have lower

power requirements

• x8 DIMMs (x8 data width of rank) will generally draw less power than equivalently sized x4 DIMMs

Memory

Controller-1

QPI

Co

re

5

Co

re

6

Co

re

7

Co

re

8

Co

re

1

Co

re

2

Co

re

3

Co

re

4

24MB L3 Cache

Memory

Controller-2

Mill

Brook 1

Mill

Brook 2

Mill

Brook 3

Mill

Brook 4

SMI 4

SMI 1

SMI 2

SMI 3

QPI (x4)

Memory

Controller-3

QPI

Co

re

5

Co

re

6

Co

re

7

Co

re

8

Co

re

1

Co

re

2

Co

re

3

Co

re

4

24MB L3 Cache

Memory

Controller-4

Mill

Brook 5

Mill

Brook 6

Mill

Brook 7

Mill

Brook 8

SMI 8

SMI 5

SMI 6

SMI 7