DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

148 of 344

Register Name:

BSRL

Register Description:

BERT Status Register Latched

Register Address:

8Eh

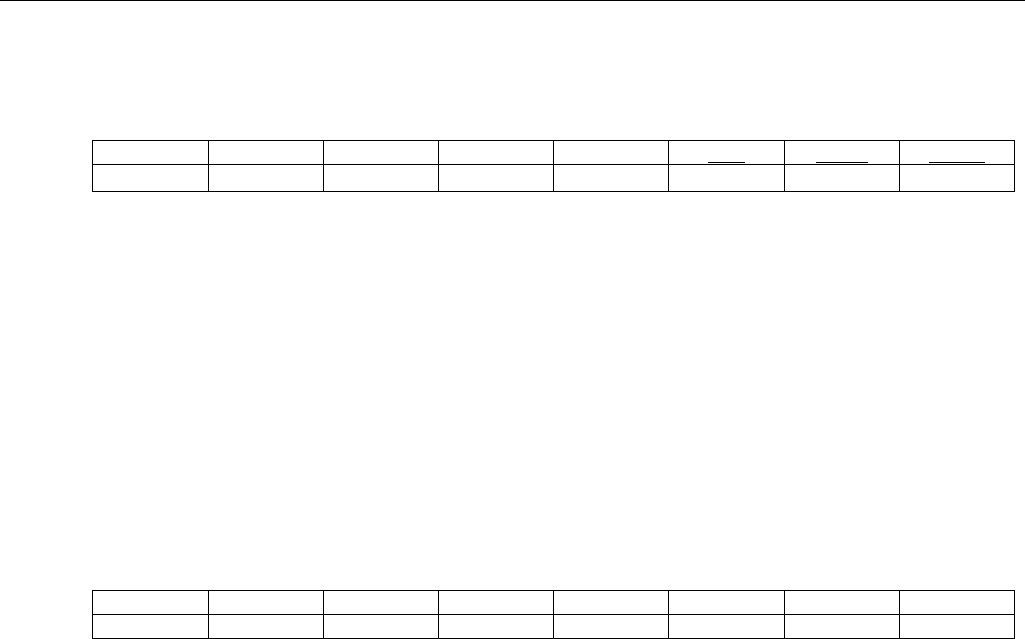

Bit # 7 6 5 4 3 2 1 0

Name - - - - PMSL

BEL BECL OOSL

Default - - - - - - - -

Bit 3: Performance Monitor Update Status Latched (PMSL) This bit is set when the PMS bit transitions from 0

to 1.

Bit 2: Bit Error Detected Latched (BEL) This bit is set when a bit error is detected.

Bit 1: Bit Error Count Latched (BECL) This bit is set when the BEC bit transitions from 0 to 1.

Bit 0: Out Of Synchronization Latched (OOSL) This bit is set when the OOS bit changes state.

Register Name:

BSRIE

Register Description:

BERT Status Register Interrupt Enable

Register Address:

90h

Bit # 7 6 5 4 3 2 1 0

Name - - - - PMSIE BEIE BECIE OOSIE

Default 0 0 0 0 0 0 0 0

Bit 3: Performance Monitoring Update Status Interrupt Enable (PMSIE) This bit enables an interrupt if the

PMSL bit is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 2: Bit Error Interrupt Enable (BEIE) This bit enables an interrupt if the BEL bit is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 1: Bit Error Count Interrupt Enable (BECIE) This bit enables an interrupt if the BECL bit is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 0: Out Of Synchronization Interrupt Enable (OOSIE) This bit enables an interrupt if the OOSL bit is set.

0 = interrupt disabled

1 = interrupt enabled