DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

224 of 344

Register Name:

TR.IMR5

Register Description:

Interrupt Mask Register 5

Register Address:

1Fh

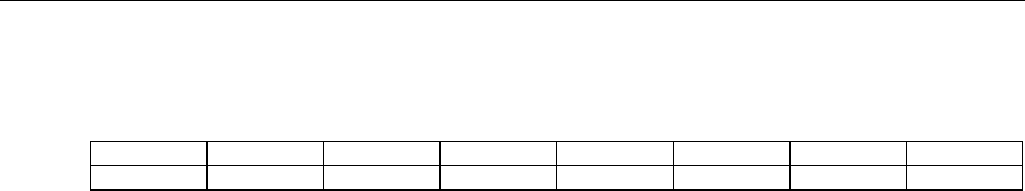

Bit # 7 6 5 4 3 2 1 0

Name — — TESF TESEM TSLIP RESF RESEM RSLIP

Default 0 0 0 0 0 0 0 0

Bit 5: Transmit Elastic Store Full Event (TESF)

0 = interrupt masked

1 = interrupt enabled

Bit 4: Transmit Elastic Store Empty Event (TESEM)

0 = interrupt masked

1 = interrupt enabled

Bit 3: Transmit Elastic Store Slip-Occurrence Event (TSLIP)

0 = interrupt masked

1 = interrupt enabled

Bit 2: Receive Elastic Store Full Event (RESF)

0 = interrupt masked

1 = interrupt enabled

Bit 1: Receive Elastic Store Empty Event (RESEM)

0 = interrupt masked

1 = interrupt enabled

Bit 0: Receive Elastic Store Slip-Occurrence Event (RSLIP)

0 = interrupt masked

1 = interrupt enabled