8254B COUNTER 1 DATA - USER COUNTER #5

BADR3 + 9

READ/WRITE

D0D1D2D3D4D5D6D7

01324567

The clock, gate and output lines of Counter 1 are available to the user at the 100-pin connector as User Counter 5.

The Counter 1 clock source is always external and must be provided by the user. The buffered version of the inter-

nal 10-MHz clock available at the user connector may be used as the clock source

.

8254B COUNTER 2 DATA - USER COUNTER #6

BADR3 + Ah

READ/WRITE

D0D1D2D3D4D5D6D7

01324567

The clock, gate and output lines of Counter 2 are available to the user at the 100-pin connector as User Counter 6.

The Counter 2 clock source is always external and must be provided by the user. The buffered version of the inter-

nal 10-MHz clock available at the user connector may be used as the clock source

.

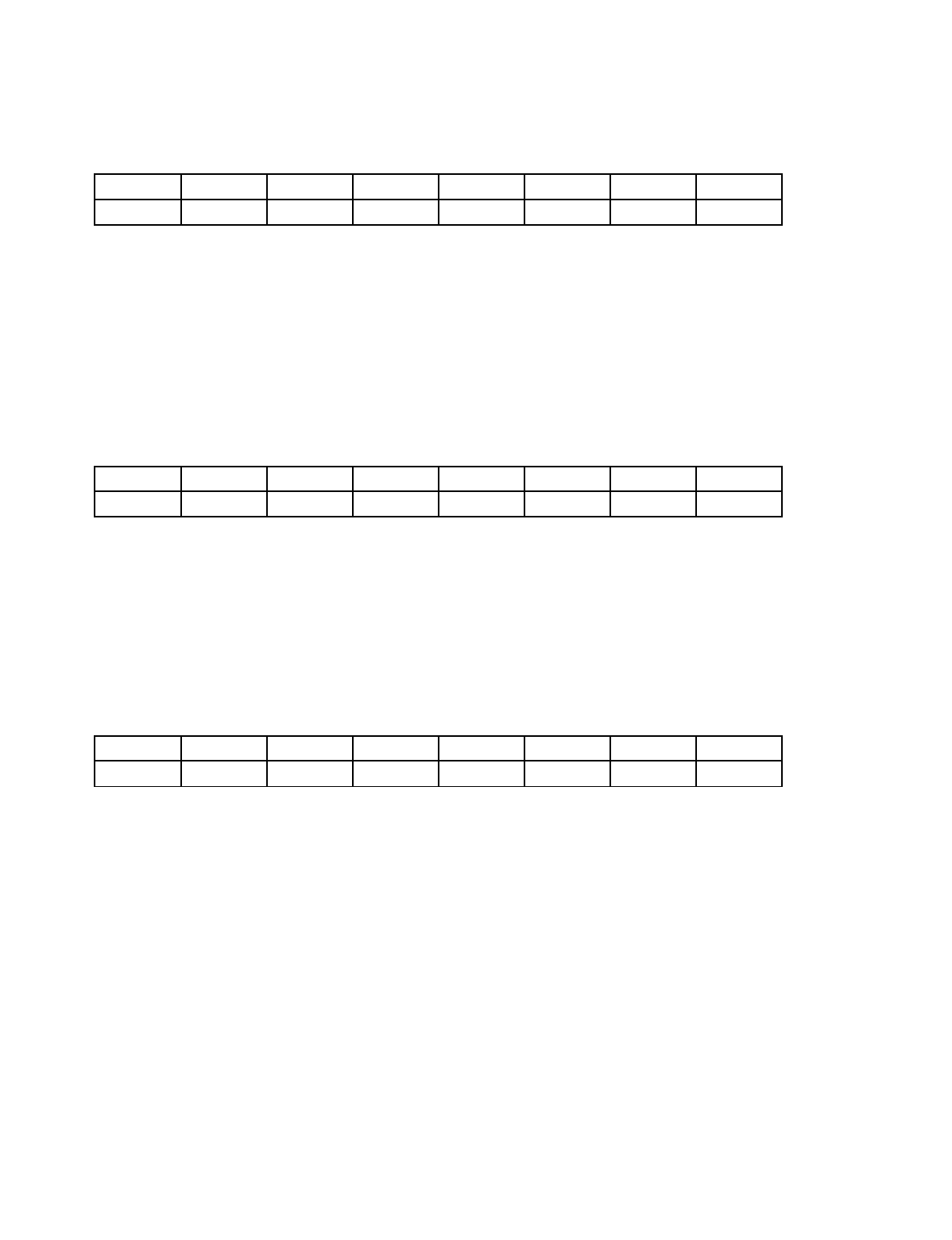

8254B CONTROL REGISTER

BADR3 + Bh

WRITE ONLY

D0D1D2D3D4D5D6D7

01324567

The control register is used to set the operating Modes of 8254B Counters 0,1 & 2. A counter is configured by

writing the correct Mode information to the Control Register, then the proper count data must be written to the

specific Counter Register.

The Counters on the 8254 are 16-bit devices. Since the interface to the 8254 is only 8-bits wide, Count data is

written to the Counter Register as two successive bytes. First the low byte is written, then the high byte. The Control

Register is 8-bits wide. Further information can be obtained on the 8254 data sheet, available from Intel or Harris.

32