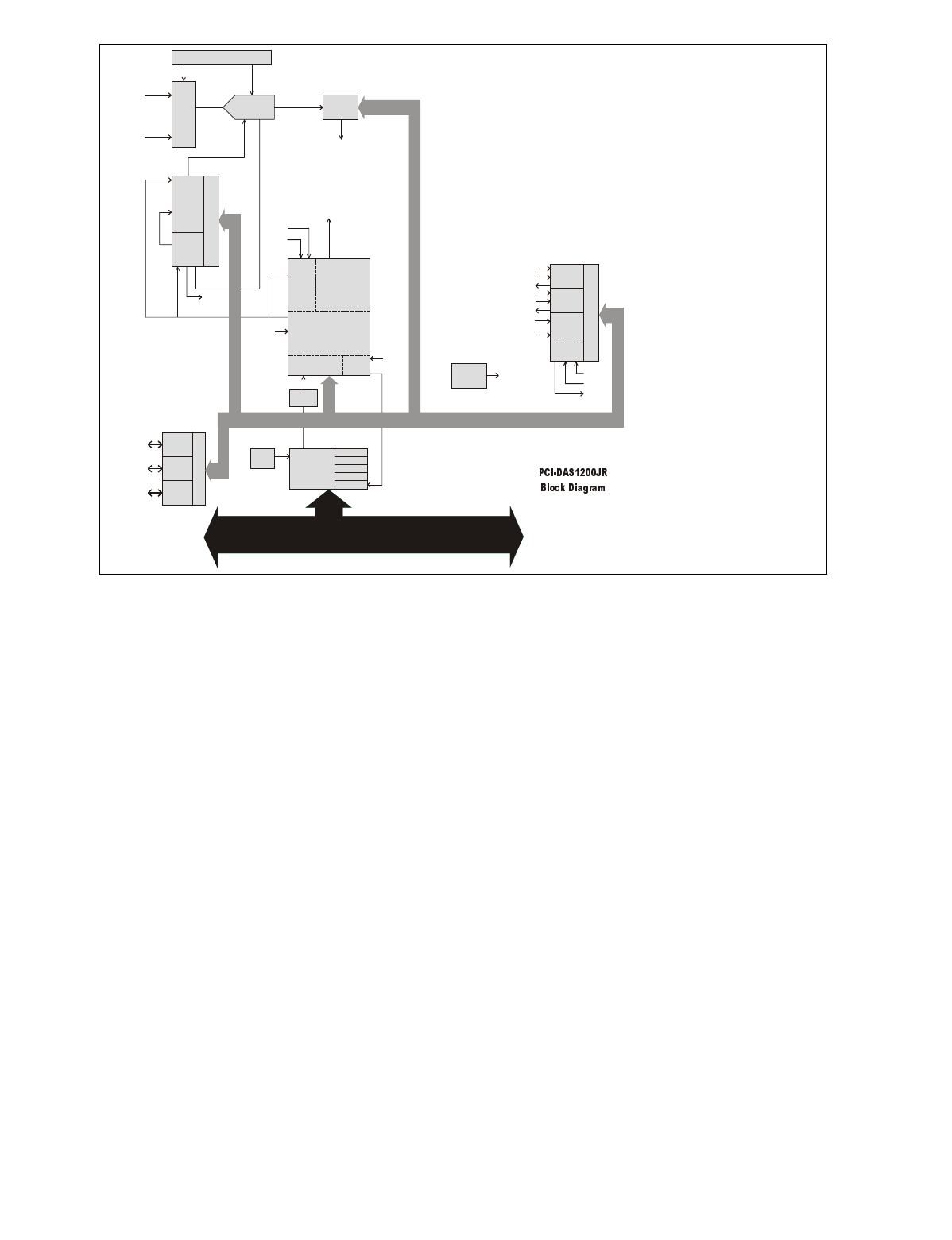

Port A

Port B

Port C

Control

PA (7:0)

PB (7:0)

PC (7:0)

Digital I/O

8

PCI

CONTROLLER

BADR1

BADR2

BADR3

BADR4

Interrupt

Boot

EEPROM

ADC

Pacer

Control

Scan

&

Burst

Logic

Trigger

Control

Decode/Status

Int

Ctl

Bus

Timing

INT

Gains = 1, 2, 4, 8

XTRIG

CONTROLLER

FPGA

ADC

Pacer

CTR 2

CTR 1

Sample

Counter

CTR0

Control

Gain and Offset Autocal

INT

12-Bit, 330KHz

Mux

&

Gain

Analog In

16 CH S.E.

8 CH DIFF.

1024 x 12

FIFO

CTR1

ADC

Index

Counter

User

CTR 0

Control

Time Base

GATE

CLK

OUT

INT

XTRIG

Start EOC

INT

10MHz

LOCAL BUS

PCI BUS (5V, 32-BIT, 33MHZ)

Burst/Scan

Burst/Scan

EXT PCR

10 MHz

CTR2

CLK2

GATE2

OUT2

CLK1

GATE1

OUT1

2