Intel® SHG2 DP Server Board Technical Product Specification Processor and Chipset

Revision 1.0 Intel Order Number C11343-001

13

2.4.6 Power Management

One of the embedded functions of CSB5 is a power management controller. The SHG2 server

board uses this to implement ACPI-compliant power management features. The SHG2

supports four sleep states: S0, S1, S4, and S5.

2.4.7 General Purpose Input and Output Pins

The CSB5 provides a number of general-purpose input (GPI) and general-purpose output

(GPO) pins. Many of these pins have alternate functions, and thus all are not available. Table 2

lists the GPI and GPO pins used on the SHG2 baseboard and gives a brief description of their

function.

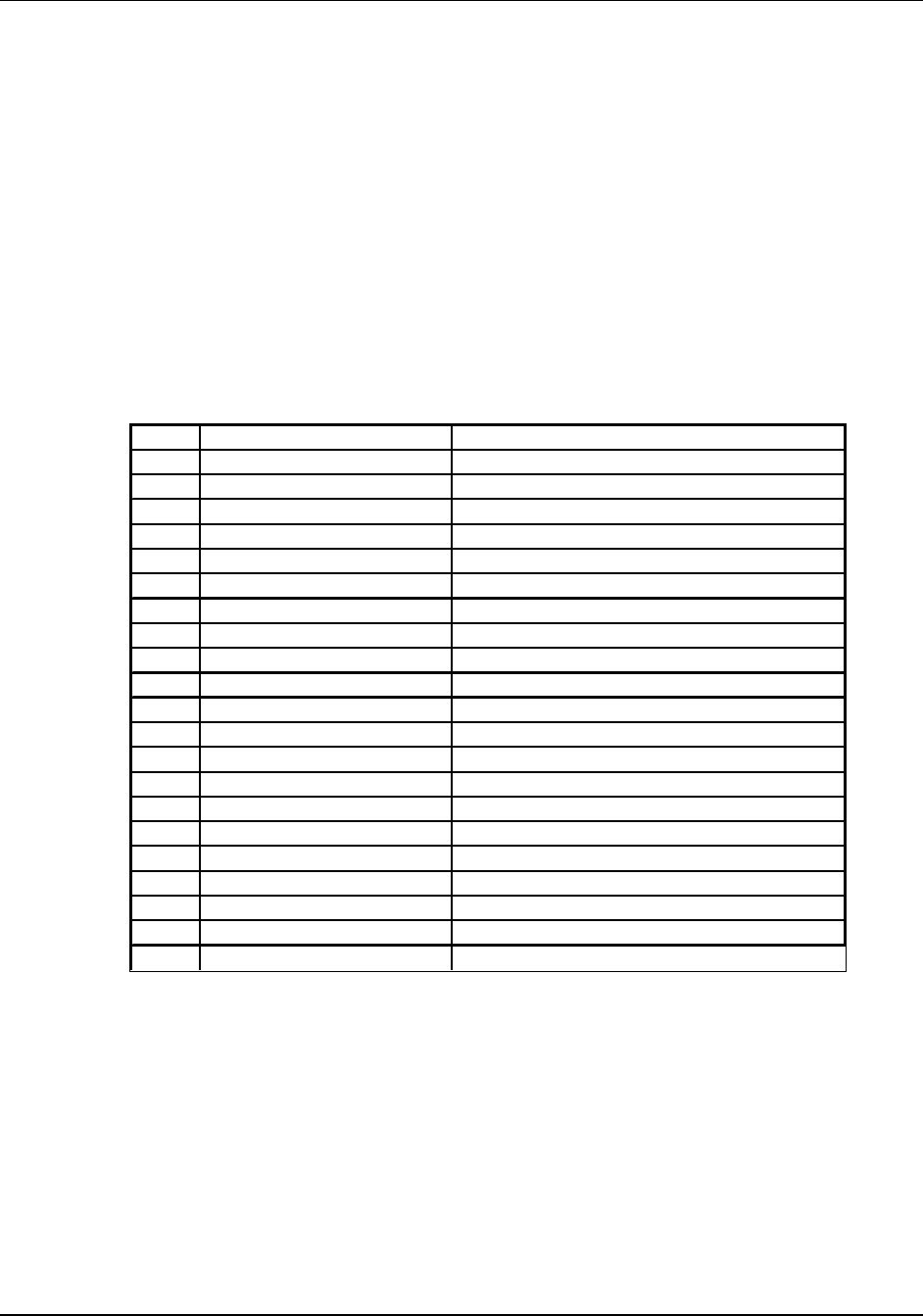

Table 2. CSB5 GPIO Usage Table

Pad Usage Description

V3 CMIC_FATALN CMIC fatal error condition

W2 CMIC_ALERTN CMIC error condition

W3 SCSI_IDSEL_EN SCSI ID select enable

W4 CIOB1_ALERTN CIOB error condition

Y4 CSB5_NMI CSB5 NMI condition

Y1 BMC_IRQ_SMI-10 BMC SMI condition

Y2 LAN1_IDSEL_EN LAN1 ID select enable

Y19 NVRAMCLR Non-volatile RAM clear status

V17 PASSDIS-00 Allows password to be disabled

U16 CMOSCLR-00 CMOS clear status

V15 VENDER_SEL Monitor PCIRST# signal

T20 F3SETUPEN-00 Enable Inspection Mode for factory use

T19 BMC_SCI-10 BMC system control interrupt status

T18 BMCISPMD-00 Reserved

Y16 SIDE_A+000 Secondary IDE addressbit 0

V12 SIDE_A+001 Secondary IDE address bit 1

U12 SIDE_A+002 Secondary IDE address bit 2

V19 LAN2_IDSEL_EN LAN2 ID select enable

W20 VGA_IDSEL_EN Video ID select enable

U14 FRWPN Enable Frimware Write Protect Mode

Y20 ROM_CSN BIOS flash chip select