Intel® SHG2 DP Server Board Technical Product Specification Error Reporting and Handling

Revision 1.0 Intel Order Number C11343-001

43

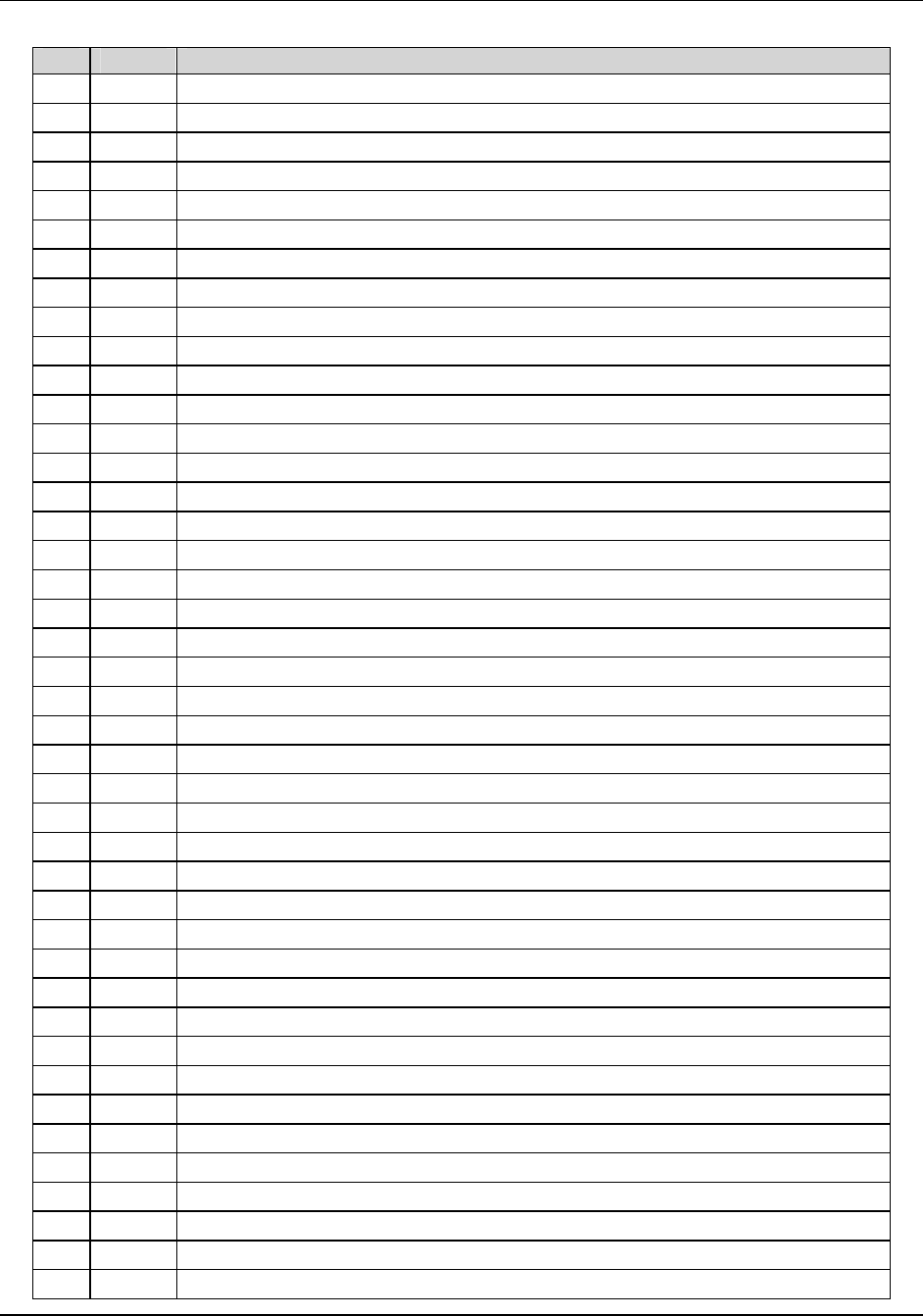

CP Beeps Reason

7C Set up hardware interrupt vectors

7D Intelligent system monitoring

7E Test coprocessor if present

82 Detect and install external RS232 ports

85 Initialize PC-compatible PnP ISA devices

86 Re-initialize on board I/O ports

88 Initialize BIOS Data Area

8A Initialize Extended BIOS Data Area

8C Initialize floppy controller

90 Initialize hard disk controller

91 Initialize local bus hard disk controller

92 Jump to UserPatch2

93 Build MPTABLE for multi-processor boards

94 Disable A20 address line

95 Install CD-ROM for boot

96 Clear huge ES segment register

98 1-2 Search for option ROMs. One long, two short beeps on checksum failure

9A Shadow option ROMs

9C Set up Power Management

9E Enable hardware interrupts

A0 Set time of day

A2 Check key lock

A4 Initialize typematic rate

A8 Erase F2 prompt

AA Scan for F2 key stroke

AC Enter SETUP

AE Clear in-POST flag

B0 Check for errors

B2 POST done – prepare to boot Operating System

B4 1 One short beep before boot

B5 Display MultiBoot menu

B6 Check password, password is checked before option ROM scan

B7 ACPI initialization

B8 Clear global descriptor table

BC Clear parity checkers

BE Clear screen (optional)

BF Check virus and backup reminders

C0 Try to boot with INT 19

C8 Forced shutdown

C9 Flash recovery

DO Interrupt handler error

D2 Unknown interrupt error