Philips Semiconductors

User’s Manual - Preliminary -

P89LPC906/907/908

INTERRUPTS

2003 Dec 8 32

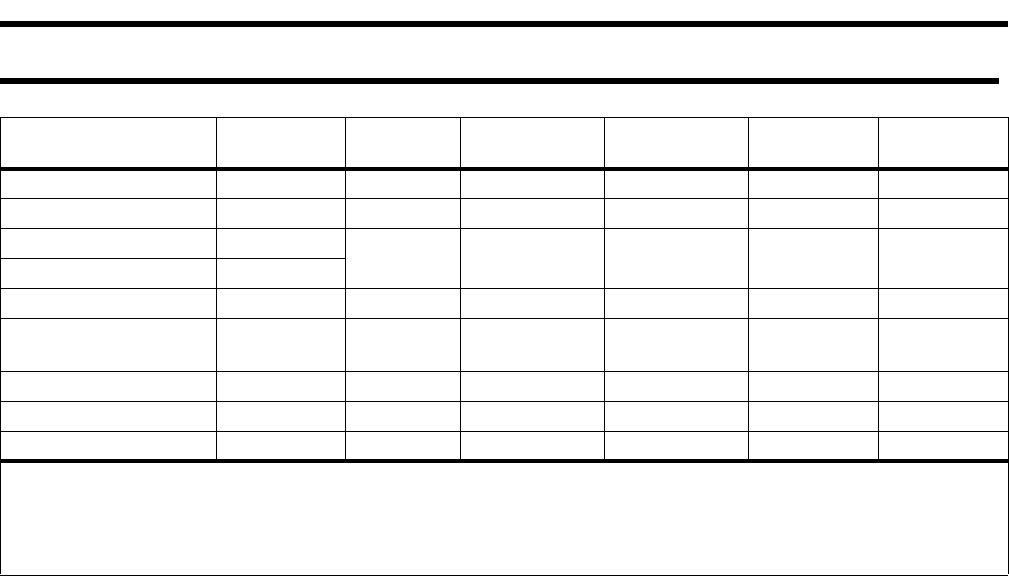

Table 3-3: Summary of Interrupts - P89LPC907,P89LPC908

EXTERNAL INTERRUPT INPUTS

The P89LPC906/907/908 have a Keypad Interrupt function (see Keypad Interrupt (KBI) on page 77). This can be used as an

external interrupt input. If enabled when the P89LPC906/907/908 is put into Power down or Idle mode, the keypad interrupt will

cause the processor to wake up and resume operation. Refer to the section on Power Reduction Modes for details.

EXTERNAL INTERRUPT PIN GLITCH SUPPRESSION

Most of the P89LPC906/907/908 pins have glitch suppression circuits to reject short glitches (please refer to the P89LPC906/

907/908 datasheet, AC Electrical Characteristics for glitch filter specifications) .

Description

Interrupt

Flag Bit(s)

Vector

Address

Interrupt

Enable Bit(s)

Interrupt

Priority

Arbitration

Ranking

Power down

Wakeup

Timer 0 Interrupt TF0 000Bh ET0 (IEN0.1) IP0H.1, IP0.1 3 No

Timer 1 Interrupt TF1 001Bh ET1 (IEN0.3) IP0H.3, IP0.3 5 No

Serial Port Tx and Rx

1,3

TI & RI

0023h

ES/ESR

(IEN0.4)

IP0H.4, IP0.4 8 No

Serial Port Rx

1,3

RI

Brownout Detect BOF 002Bh EBO (IEN0.5) IP0H.5, IP0.5 1 Yes

Watchdog Timer/Real-

time Clock

WDOVF/

RTCF

0053h

EWDRT

(IEN0.6)

IP0H.6, IP0.6 2 Yes

KBI Interrupt KBIF 003Bh EKBI (IEN1.1) IP1H.1, IP1.1 4 Yes

Comparator interrupt CMF 0043h EC (IEN1.2) IP1H.2, IP1.2 6 Yes

Serial Port Tx

2

TI 006Bh EST (IEN1.6) P1H.6, IP1.6 7 No

1. SSTAT.5 = 0 selects combined Serial Port (UART) Tx and Rx interrupt; SSTAT.5 = 1 selects Serial Port Rx interrupt only

(Tx interrupt will be different, see Note 3 below).

2. This interrupt is used as Serial Port (UART) Tx interrupt if and only if SSTAT.5 = 1, and is disabled otherwise. Although the

P89LPC907 does not have the RxD pin, this function is still available to allow switching the Tx interrupt vector.

3. If SSTAT.0 = 1, the following Serial Port additional flag bits can cause this interrupt: FE, BR, OE