S3C8275X/F8275X/C8278X/F8278X/C8274X/F8274X INTERRUPT STRUCTURE

5-7

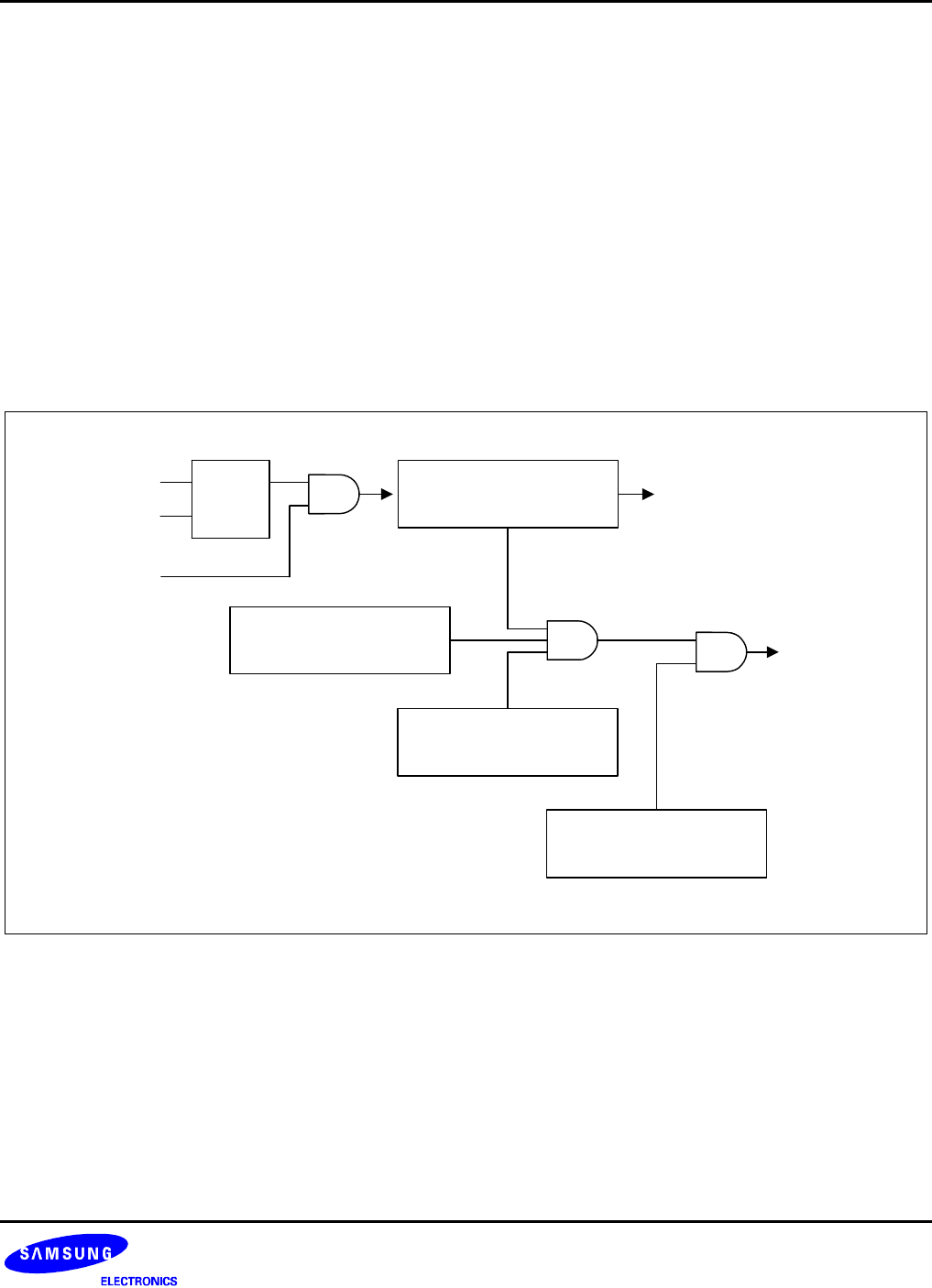

INTERRUPT PROCESSING CONTROL POINTS

Interrupt processing can therefore be controlled in two ways: globally or by specific interrupt level and source. The

system-level control points in the interrupt structure are:

— Global interrupt enable and disable (by EI and DI instructions or by direct manipulation of SYM.0 )

— Interrupt level enable/disable settings (IMR register)

— Interrupt level priority settings (IPR register)

— Interrupt source enable/disable settings in the corresponding peripheral control registers

NOTE

When writing an application program that handles interrupt processing, be sure to include the necessary

register file address (register pointer) information.

Interrupt Request Register

(Read-only)

IRQ0-IRQ7,

Interrupts

Interrupt Mask

Register

Polling

Cycle

Interrupt Priority

Register

Global Interrupt Control (EI,

DI or SYM.0 manipulation)

S

R

Q

nRESET

EI

Vector

Interrupt

Cycle

Figure 5-4. Interrupt Function Diagram