LZT 123 1836 61

5.13 Memory Card Interface (SD/MMC) [to be implemented in a future release]

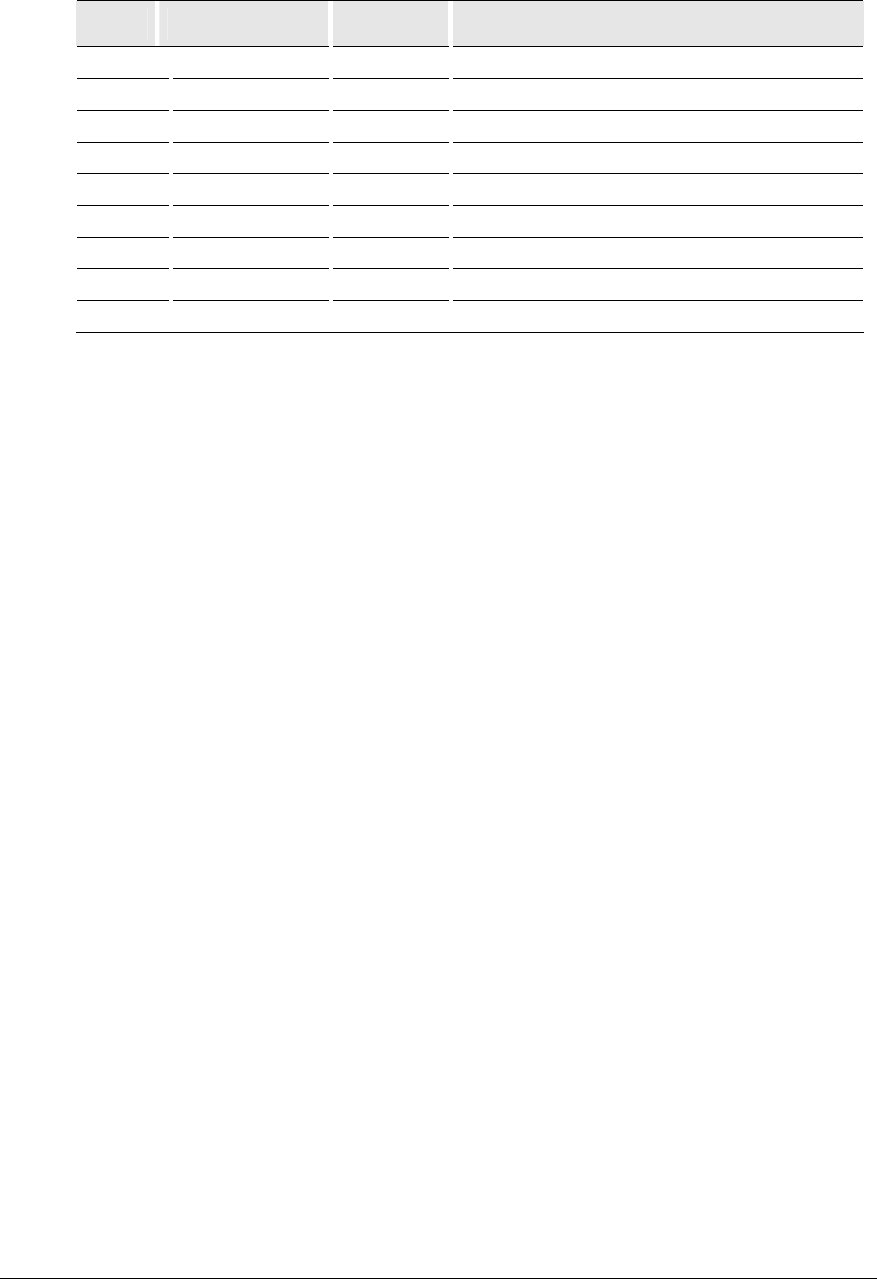

Pin Name Direction Function

74 MMCCLK Output SD/MMC card clock

75 MMCCMD In/Out SD/MMC card command/response

76 MMCDAT0 In/Out SD/MMC card data 0

77 MMCDAT1 In/Out SD/MMC card data 1

78 MMCDAT2 In/Out SD/MMC card data 2

79 MMCDAT3 In/Out SD/MMC card data 3

80 MMCMD_EN Output SD/MMC card command enable

81 MMCDAT_EN Output SD/MMC card data enable (data 1-3)

82 MMCDAT_EN0 Output SD/MMC card data enable (data 0)

SD/MMC interface module acts as either a multimedia card bus host or a secure

digital memory card bus host. The interface conforms to the following standards:

• Multimedia Card Specification v2.11

• Secure Digital Memory Card Physical Layer Specification v0.96

The SD/MMC interface provides around 800kbps net throughput.

The SD/MMC interface, like all IO in the module, is 1.8V. In order to interface to

some SD/MMC devices based on 3V technology it is necessary to level shift these

signals for compatibility purposes. The MMC MD & DAT enable signals (pins 80, 81,

82) are provided to configure level shifters for directivity, which may be used with the

Agere PSC2217 level shifter for example. There are other means of level shifting

using bi-directional level shifters which do not require direction pins, such as:

• Philips GTL2002, 2-bit bidirectional low voltage translators

• Maxim MAX3001E, 8-channel bidirectional level translators

5.13.1 Multimedia Card System

The multimedia card system transfers commands and data using three signal lines

on a single physical bus:

• MMCCLK: One bit is transferred on both command and data lines with each clock

cycle. The clock frequency varies between 0 MHz and 20 MHz for a multimedia

card.