Hardware Setup

SY-5EHM/5EH5 V1.3

21

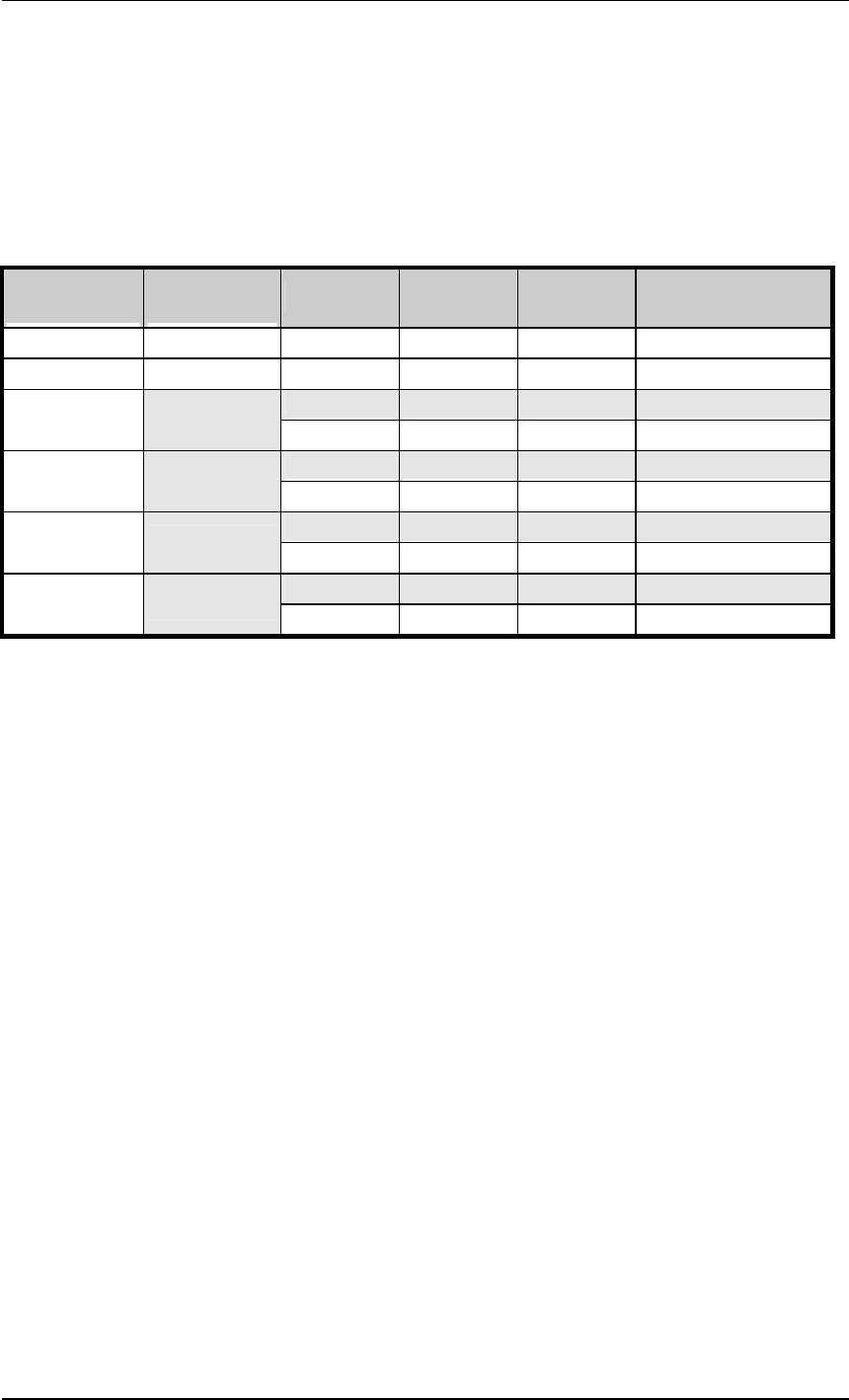

Step 5. Set JP7,JP9,JP10 for SDRAM frequency

JP7 is used to indicate the frequency of the CPU bus clock to the ETEQ

chipset.

JP9 and JP10 are used to determine that the SDRAM is running at the

frequency of the CPU bus clock or the AGP clock.

CPU BUS

Clock

AGP BUS

Clock

JP10 JP7 JP9 SDRAM Clock

66MHz 66MHz 1-2 2-3 2-3 66MHz

75MHz 75MHz 1-2 2-3 2-3 75MHz

2-3 1-2 1-2 55MHz

83MHz 55MHz

1-2 1-2 2-3 83MHz

2-3 1-2 1-2 63.4MHz

95MHz 63.4MHz

1-2 1-2 2-3 95MHz

2-3 1-2 1-2 63.4MHz

97MHz 63.4MHz

1-2 1-2 2-3 95MHz

2-3 1-2 1-2 66MHz

100MHz 66MHz

1-2 1-2 2-3 100MHz

Note: Use 8ns or faster SDRAM modules (PC100 compliant) when

SDRAM is set to run at the frequency of 95/100 MHz.