8.4.11InterruptPriorityRegister0(INTPRI0)

8.4.12InterruptPriorityRegister1(INTPRI1)

AINTCRegisters

www.ti.com

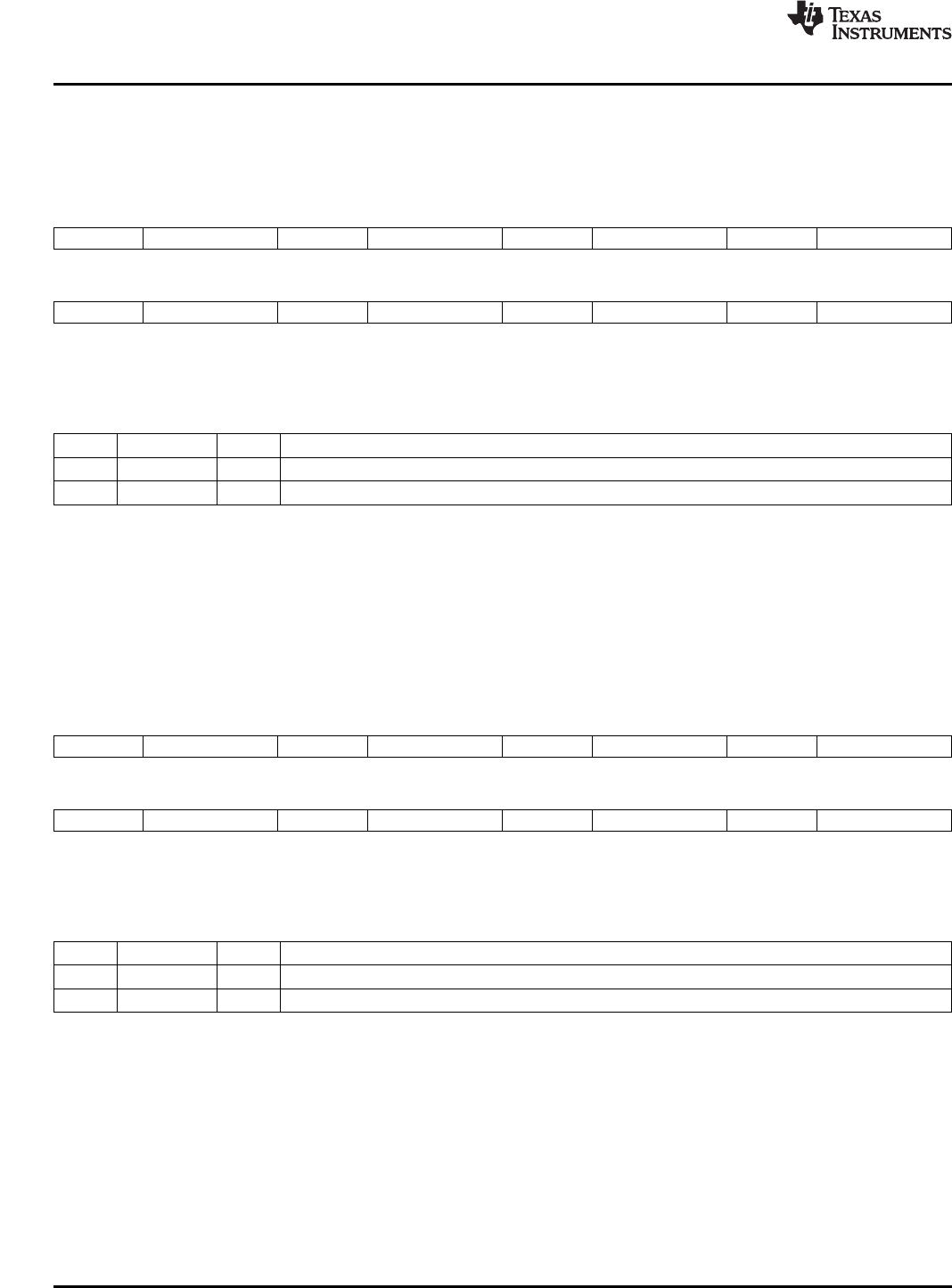

Theinterruptpriorityregister0(INTPRI0)isshowninFigure8-15anddescribedinTable8-13.

Figure8-15.InterruptPriorityRegister0(INTPRI0)

313028272624232220191816

ReservedINT7ReservedINT6ReservedINT5ReservedINT4

R-0R/W-7hR-0R/W-7hR-0R/W-7hR-0R/W-7h

15141211108764320

ReservedINT3ReservedINT2ReservedINT1ReservedINT0

R-0R/W-7hR-0R/W-7hR-0R/W-7hR-0R/W-7h

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table8-13.InterruptPriorityRegister0(INTPRI0)FieldDescriptions

BitFieldValueDescription

Reserved0Reserved

INTn0-7hSelectsINTnprioritylevel.

Theinterruptpriorityregister1(INTPRI1)isshowninFigure8-16anddescribedinTable8-14.

Figure8-16.InterruptPriorityRegister1(INTPRI1)

313028272624232220191816

ReservedINT15ReservedINT14ReservedINT13ReservedINT12

R-0R/W-7hR-0R/W-7hR-0R/W-7hR-0R/W-7h

15141211108764320

ReservedINT11ReservedINT10ReservedINT9ReservedINT8

R-0R/W-7hR-0R/W-7hR-0R/W-7hR-0R/W-7h

LEGEND:R/W=Read/Write;R=Readonly;-n=valueafterreset

Table8-14.InterruptPriorityRegister1(INTPRI1)FieldDescriptions

BitFieldValueDescription

Reserved0Reserved

INTn0-7hSelectsINTnprioritylevel.

ARMInterruptController(AINTC) 98SPRUEP9A–May2008

SubmitDocumentationFeedback