Chapter 4 Register Structure and Format 37

4.6 MUX ControlBASE+4 and BASE+5

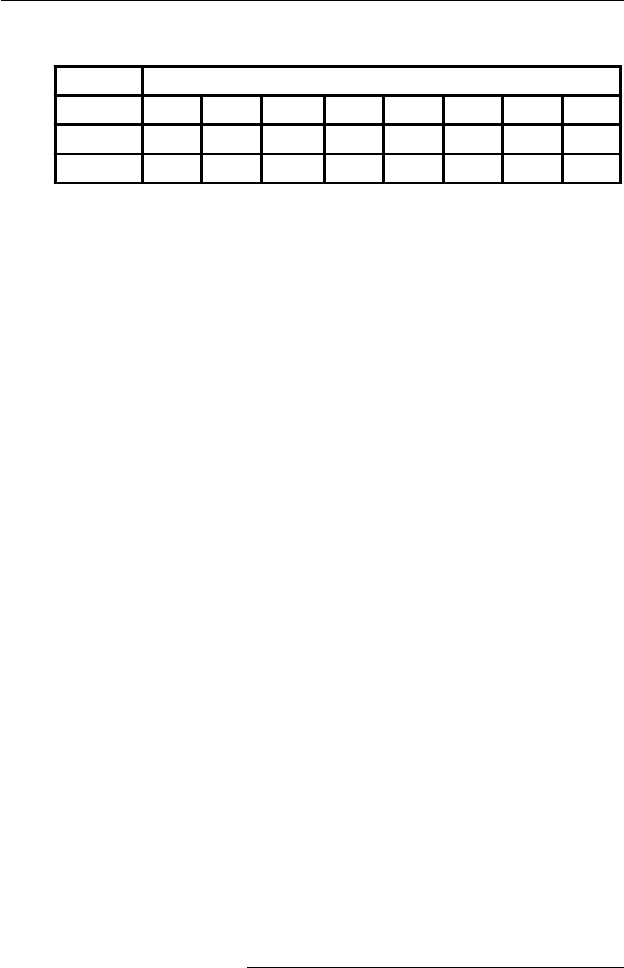

Table 4.6: The register for multiplexer control

CL3 ~ CL0 Start Scan Channel Number

CH3 ~ CH0 Stop Scan Channel Number

BASE+4 bit 3 to bit 0, CL3 ~ CL0, act as a pointer when you program

the A/D channel setting (see previous section). When you set the

MUX start channel to an analog input channel, AIn ( n = 0, 1, 2…15 ),

the gain code, B/U and S/D written to the register of BASE+2, is for

channel n.

Caution! We recommend you set the same start and stop

channel when writing to the register BASE+2.

Otherwise, if the A/D trigger source is on, the

multiplexer will continuously scan between channels

and the range setting may be set to an unexpected

channel. Make sure the A/D trigger source is turned

off to avoid this kind of error.

The write-only registers of BASE +4 and BASE+5 control how the

multiplexers (MUXs) scan. BASE+4 bit 3 to bit 0, CL3 ~ CL0, hold

the start scan channel number, and BASE+5 bit 3 to bit 0, CH3 ~ CH0,

hold the stop scan channel number. Writing to these two registers

automatically initializes the scan range of the MUXs. Each A/D

conversion trigger also sets the MUXs to the next channel. With

continuous triggering, the MUXs will scan from the start channel to

Write MUX Control

Bit # 7 6 5 4 3 2 1 0

BASE+5 CH3 CH2 CH1 CH0

BASE+4 CL3 CL2 CL1 CL0