5

24332E—December 2002 AMD Athlon™ Processor Model 6 Revision Guide

Preliminary Information

1 Product Errata

This section documents AMD Athlon™ Processor Model 6 product errata. The errata are divided into

categories to assist referencing particular errata. A unique tracking number for each erratum has been

assigned within this document for user convenience in tracking the errata within specific revision

levels. Table 1 cross-references the revisions of the processor to each erratum. An “X” indicates that

the erratum applies to the stepping. The absence of an “X” indicates that the erratum does not apply

to the stepping. Table 2 on page 6 cross-references erratum to each processor segment. An “X”

indicates that the erratum applies to the processor segment.

Note: There can be missing errata numbers. Errata that have been resolved from early revisions of the

processor have been deleted, and errata that have been reconsidered may have been deleted or

renumbered.

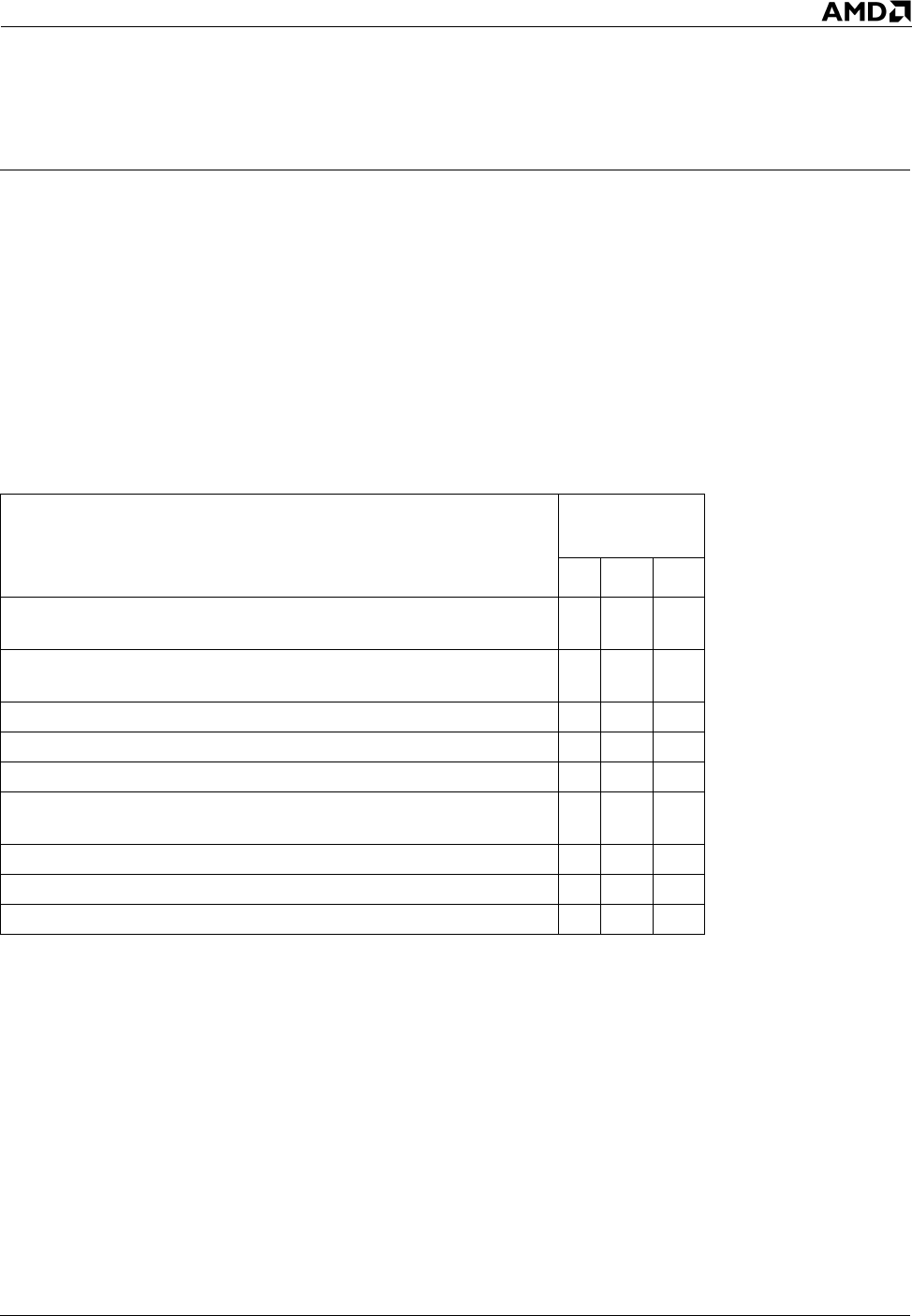

Table 1. Cross-Reference of Product Revision to Errata

Errata Numbers and Description

Revision

Numbers

A0 A2 A5

16 INVLPG Instruction Does Not Flush Entire Four-Megabyte Page Properly with

Certain Linear Addresses

XX

17 Deadlock May Occur in a Two-Processor System in the Presence of Probe to

Memory- Mapped I/O

XX X

18 Processor May Issue Non-Connect Bus Cycle After FID Special Cycle X X

19 Processor Does Not Support Reliable Microcode Patch Mechanism X

20 Processor Performance Counters Do Not Count Some x86 Instructions X X X

21 A Speculative SMC Store Followed by an Actual SMC Store May Cause One-

Time Stale Execution

XX X

22 Real Mode RDPMC with Illegal ECX May Cause Unpredictable Operation X X X

23 Using Task Gates With Breakpoints Enabled May Cause Unexpected Faults X X X

24 Single Step Across I/O SMI Skips One Debug Trap X X X