CHAPTER 1

Hardware

Color LCD Interface

9

The RAM expansion slot is located on the RAM/ROM board, and supports up to 10 MB

of PSRAM, for a total of 14 MB. See the “RAM Expansion Interface” section on page 10

for information about designing RAM expansion cards.

RAM is always contiguous because only one size of RAM chip (4 Mbits) is used. As a

result, software does not have to “stitch” memory. The RAM array is located in the

system memory map between addresses $0000 0000 and $00DF FFFF, except following a

system reset or sleep cycle, when it is overlaid by system ROM. However, the overlay is

removed following access to normal ROM space, and the RAM space is then accessible.

Both RAM and ROM memory spaces provide DSACK signals to the processor even if

memory is not actually installed. The RAM data path is 32 bits wide.

RAM Wait States 1

RAM accesses require 2 wait states when using 85 ns PSRAM exclusively. Installing

100 ns expansion RAM causes the memory controller to insert an additional wait state in

all memory accesses (both main and expansion).

Battery Backup 1

Both main and expansion RAM are backed up when the computer is in the sleep state, as

long as the battery is charged or the power adapter is plugged in. RAM contents are not

maintained when the computer is turned off or when the battery is removed.

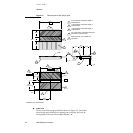

Color LCD Interface 1

The color display circuitry in the Macintosh PowerBook 165c emulates a NuBus video

card installed in slot $C. This circuitry includes the LCD controller chip set, 512 KB of

DRAM, and a declaration ROM. The PowerBook 165c is compatible with software that

uses QuickDraw and the Palette Manager. Color table animation is also supported.

The LCD controller chip set consists of the WD90C26 controller and WD90C55 display

driver, both made by Western Digital, and the Pangola bus interface chip, an Apple

custom ASIC that translates signals between the WD90C26 and the 68030 bus. Pangola

also handles the frame buffer conversion necessary to support 1-, 2-, and 4-bit color

modes with the Western Digital controller.

The WD90C26 contains a 256-entry CLUT, RAMDAC, frame buffer controller, and flat

panel control circuitry. Although the CLUT supports a palette of 262,143 colors, many of

the possible colors do not look acceptable on the display. Due to the nature of LCD

technology, some colors are dithered or exhibit noticeable flicker. Apple has developed a

new gamma table for this display that minimizes flicker and optimizes available colors.

With this gamma table in place, the effective range of the CLUT is 4096 colors.

The frame buffer appears to the 68030 as a continuous RAM array of 512 KB beginning at

$FC04 0000. The data path is 16 bits wide and byte addressable. The frame buffer is

controlled by the WD90C26, which allocates 1 byte per pixel in all color modes. Because