Chapter 4 139

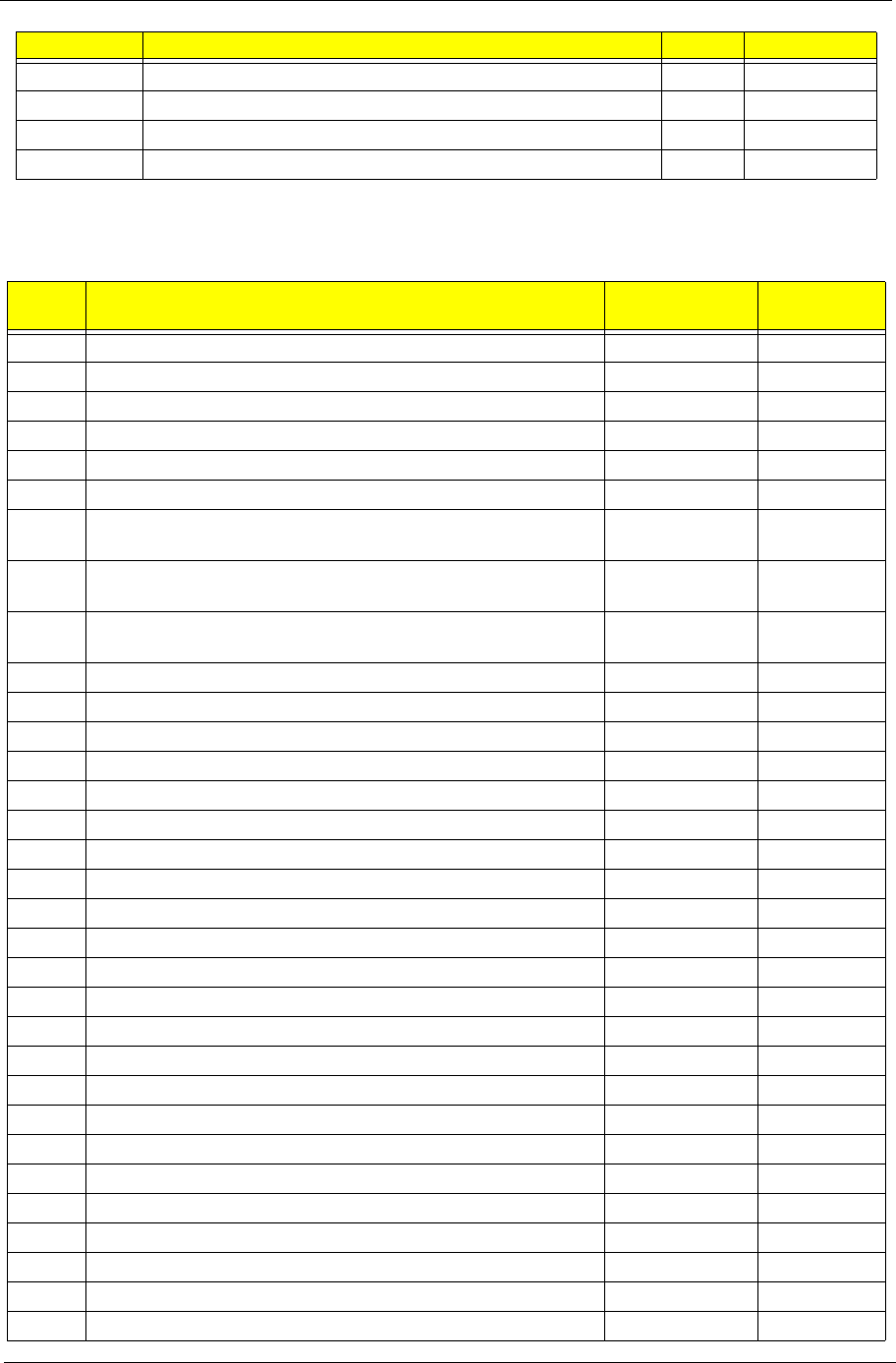

Core POST Code Table

The following table details the core POST codes and functions used in SecureCore.

0xA0xx Launch BIOS ACMSclean PEI chipset/MRC

0xA4xx Launch BIOS ACMScheck PEI chipset/MRC

0xE5 Wait for ME ready DXE HECI/iAMT

0xE6 ME Ready DXE HECI/iAMT

POST

Code

Function Phase Component

0x00 Early Microcode update for CAR CEI / SEC Core

0x01 Enable CAR CEI / SEC Core

0x02 CAR Done, initial stack CEI / SEC Core

0xEE unknown CPU ID to load uCode CEI / SEC CPU

0xEF unknown DT CPU to load uCode CEI / SEC CPU

0xnn File count found in a volume PEI Core

0x11 Debug Test driver for debug test PPI 1 (If install debugTest

driver)

PEI Core

0x22 Debug Test driver for debug test PPI 2 (If install debugTest

driver)

PEI Core

0x33 Debug Test driver for debug test PPI 3 (If install debugTest

driver)

PEI Core

0x44 Entry point of loadfile PEI Core

0x88 Entry point of apMuLoader PEI Core

0x80 A PEIM found PEI Core

0x82 PEIM not dispatched yet PEI Core

0x84 PEIM satisfies depex PEI Core

0x86 Image loaded but fail on security PEI Core

0x88 Executing a PEIM PEI Core

0x8A Processing notify event for newly installed PPI PEI Core

0x8C Handing off to next phase (DXE) PEI Core

0x8F Fail to hand off to next phase, system halt PEI Core

0x90 All PEIM dispatched! Going to DxeIpl PEI Core

0xCC AP Micro-code update PEI Core

0x20 S3 resume entry S3 resume Core

0x21 Start running Boot-time bootscripts S3 resume Core

0x22 Start running Run-time bootscripts S3 resume Core

0x23 End of S3 resume, jump back to Waking vector S3 resume Core

0x80 Initialize the chipset Crisis Recovery Core

0x81 Initialize the bridge Crisis Recovery Core

0x82 Initialize the CPU Crisis Recovery Core

0x89 Set Huge Segment Crisis Recovery Core

0x83 Initialize system timer Crisis Recovery Core

0x84 Initialize system I/O Crisis Recovery Core

0x88 Initialize Multi Processor Crisis Recovery Core

POST Code Function Phase Component