2-202-20

2-202-20

2-20

Chapter 2: BIOS setupChapter 2: BIOS setup

Chapter 2: BIOS setupChapter 2: BIOS setup

Chapter 2: BIOS setup

Enhanced C1 Control [Auto]Enhanced C1 Control [Auto]

Enhanced C1 Control [Auto]Enhanced C1 Control [Auto]

Enhanced C1 Control [Auto]

When set to [Auto], the BIOS will automatically check the CPU’s capability

to enable the C1E support. In C1E mode, the CPU power consumption is

lower when idle. Configuration options: [Auto] [Disabled]

CPU Internal Thermal Control [Auto]CPU Internal Thermal Control [Auto]

CPU Internal Thermal Control [Auto]CPU Internal Thermal Control [Auto]

CPU Internal Thermal Control [Auto]

Disables or sets the CPU internal thermal control.

Configuration options: [Disabled] [Auto]

Hyper-Threading Technology [Enabled]Hyper-Threading Technology [Enabled]

Hyper-Threading Technology [Enabled]Hyper-Threading Technology [Enabled]

Hyper-Threading Technology [Enabled]

Allows you to enable or disable the processor Hyper-Threading Technology.

Configuration options: [Disabled] [Enabled]

2.4.32.4.3

2.4.32.4.3

2.4.3

ChipsetChipset

ChipsetChipset

Chipset

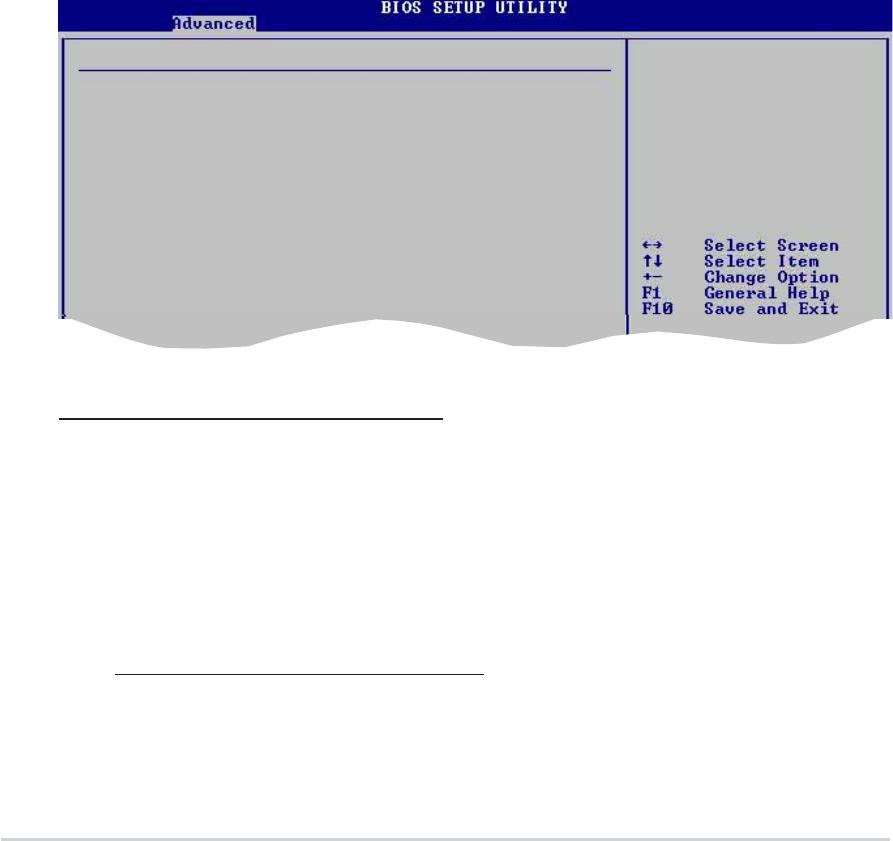

The Chipset menu allows you to change the advanced chipset settings.

Select an item then press <Enter> to display the sub-menu.

Advanced Chipset Settings

WARNING: Setting wrong values in below sections

may cause the system to malfunction.

Configure DRAM Timing by SPD [Enabled]

Performance Acceleration Mode [Auto]

DRAM Idle Timer [Auto]

DRAM Refresh Rate [Auto]

Graphic Adapter Priority [Internal VGA]

Graphics Aperture Size [ 64MB]

MPS Revision [1.4]

Advanced Chipset SettingsAdvanced Chipset Settings

Advanced Chipset SettingsAdvanced Chipset Settings

Advanced Chipset Settings

Configure DRAM Timing by SPD [Enabled]Configure DRAM Timing by SPD [Enabled]

Configure DRAM Timing by SPD [Enabled]Configure DRAM Timing by SPD [Enabled]

Configure DRAM Timing by SPD [Enabled]

When this item is enabled, the DRAM timing parameters are set according

to the DRAM SPD (Serial Presence Detect). When disabled, you can

manually set the DRAM timing parameters through the DRAM sub-items.

The following sub-items appear when this item is Disabled.

Configuration options: [Disabled] [Enabled]

DRAM CAS# Latency [2.5 Clocks]

Controls the latency between the SDRAM read command and the time

the data actually becomes available.

Configuration options: [2.0 Clocks] [2.5 Clocks] [3.0 Clocks]