A-2 Appendix

A.1 Powersupplyspecications

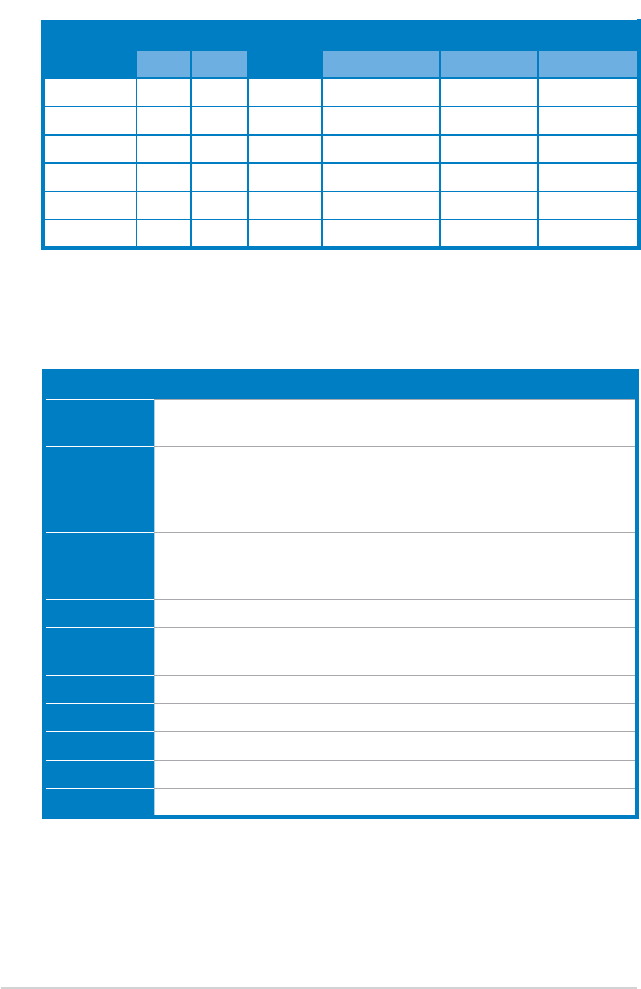

Output characteristics

Output

voltage

Load range Surge

<10ms

Regulation Ripple and noise

Min Max (%) Vpp Vpp & noise

+5V 0.3A 18A -5% ~ +5% 50mV 70mV

+3.3V 0.3A 16A -5% ~ +5% 50mV 70mV

+12V1 1A 10A 12A -5% ~ +5% 150mV 150mV

+12V2 1A 14A 18A -5% ~ +5% 150mV 150mV

-12V 0A 0.3A -10% ~ +10% 200mV 200mV

+5VSB 0.1A 2.5A -5% ~ +5% 50mV 70mV

A.2 Dubug code table

Code Description

CPU CPU initiation

Test CMOS R/W functionality

CHIP Early chipset initialization:

- Disable shadow RAM

- Disable L2 cache

- Program basic chipset registers

ddr Detect memory:

- Auto-detection of DRAM size, type and ECC

- Auto-detection of L2 cache

H A Initialize Hardware Monitor

SIO 1. Test special keyboard controller for Super I/O chips

2. Enable keyboard interface

CL- Initialize clock generator

USb Initialize USB

PS2 Initialize PS/2 Mouse

FAn Fan error

OS Boot attempt (INT 19h)