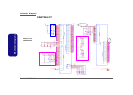

Schematic Diagrams

B - 8 CANTIGA 3/7

B.Schematic Diagrams

CANTIGA 3/7

R143

1K_1%_04

PM_THR MTRIP#3,22

DMI_R XP0 23

DFG T_VR _EN 39

DD PC_CTRLC LK

DMI_R XN0 23

M_CLK_DD R3 13

PM_D PRSLPVR24,41

MCH_RSVD1

ME TLS

Confidentiality

HD MI_CTRLCLK

R446 54.9_1%_04

R113 * 4. 02K_1%_06

DMI_R XP1 23

SM_REXT

D03-0303-2

MCH_NC_10

CLK_DREF #

R105 2.2K_04_-U

R84 *2.21K_1%_04

R72 *10mil_shor t

High: iHDMI/DP enable

1.8V

1.05VS2,3,4,5,9,10,22,25,37,39

MC H_CLKREQ#

M_ CS0 # 1 2

DFGT_VID_2 39

Z0701

MCH_CFG_5

MCH_CFG_17

MCH_RSVD14

R136 10K_04

DFGT_VID_0 39

MC H_CFG _5

R131 10K_04

M_CLK_DD R2 13

MCH_BSEL22

MCH_RSVD17

D03-0229

3.3VS

DMI_R XP3 23

HDMI_CTRLCLK 43

MCH_NC_1

MCH_CFG_20

M_ CS1 # 1 2

HDMI_CTRLCLK

MC H_HDA_SYN C 22

PM_EXTTS1#

HD MI_CTRLDA TA

MCH_NC_2

M_ ODT2 1 3

DFGT_VID_1 39

MCH_NC_25

PCI express graphics lane

reverse option for layout

convenience

MCH_NC_13

High: SDVO/iHDMI/DP enable

MCH_NC_8

R144

511_1%_04

M_CLK_DD R1# 12

MCH_RSVD25

MCH_RSVD2

C284

.1U_10V_X7R_04

MCH_NC_6

CLK_DREFSS#

DD PC_CTRLD ATA

R93 *2.21K_1%_04

MCH_CFG_15

M_ ODT0 1 2

DFGT_VID_4 39

MCH_CFG_6

SM_RCOMP_VOHMCH_RSVD23

CLK_DREF SS#

MCH_CFG_10

PCIE Loopback enable

DMI_TXP0 23

MCH_CFG_20

R489

3.01K_1%_04

M_CLK_DD R2# 13

MCH_CFG_18

DFGT_VID_3 39

R73 *2.21K_1%_04

C705

.01U_50V_X7R_04

R125 2.2K_04_-U

MCH_ CL _V REF

MPWROK 14,24,34

MCH_CFG_10

R482 80.6_1%_06

DMI_TXN3 23

R100 *2.21K_1%_04

R479 *0 _ 04 _ + U

SM_RCOMP

R478 *0 _ 04 _ + U

3.3VS

M_ ODT1 1 2

MCH_CFG_12

MCH_CFG_7

MCH_RSVD24

R605 10K_04

iTPM HOST INTERFACE

Low= enable

High=disable (default)

MCH_BSEL02

DMI_R XP2 23

MCH_RSVD15

CLK_DREFSS

C879

.01U_50V_X7R_04

PM_E XTTS1#12,13

D03-0229

DMI_TXP1 23

MCH_CLKREQ# 2

R81 33_04_-U

R490

1K_1%_04

PM_EXTTS0#

MCH_RSVD9

C707

2.2U _6.3V_06

CLK_PCIE_3GPLL# 2

MCH_CFG_13

M_CLK_DD R3# 13

CL_C LK0 24

MCH_NC_20

MCH_RSVD3

CLK_DREF

R169

1K_1%_04

1.8V9,10,12,13,14,16,37,38

H_DPR STP#3,22,41

MCH_NC_7

R75 2.21K_1%_04

MCH_NC_17

M_ CKE 3 13

R106 *2.21K_1%_04

CLK_PCIE_3GPLL 2

MCH_NC_16

MCH_NC_4

This "Daisy Chain" CMOS topology

should be routed from ICH9M to Intel

MVP, then to (G)MCH and CPU (in this

order exactly). CPU must be end agent

on the DPRSTP topology to avoid

signal integrity degradation.

M_ ODT3 1 3

MCH_NC_3

MCH_DPRSLPVR

3.3VS2,3,6,10,12, 13,14, 15,22, 23,24, 25,26,27,28,29,30, 31,32, 33,34,35,39,41, 43

MCH_CFG_9

MCH_RSVD6

R488 80.6_1%_06

R481

499_1%_04

DELAY_PWRGD24,41

MCH_NC_19

1.8V

MCH_NC_9

MCH_CFG_4

MCH_RSVD22

MCH_RSVD5

R96 *10mil_shor t

MCH_RSVD4

DDPC_CTRLDATA

R119 * 4. 02K_1%_06

D03-0227

DEL

M_ CS2 # 1 3

CLK_DREFSS 2

DMI_TXN1 23

PLT_RST#15,23

MC H_HDA_BCLK 22

M_CLK_DD R0 12

PM_EXTTS0#

R128 100_04

CL_RST#0 24

MCH _HDA_ SD I 2 2

MCH_CFG_14

CLK_DREF

MCH_CFG_16

R483 *20_1%_06

R491 1K_1%_04

DMI_R XN2 23

MCH_NC_22

MCH_RSVD11

MC H_CFG _6

VDD33,22,34,35,36,40

MCH_ TS ATN#

MCH_NC_12

MCH_NC_5

SM_RCOMP_VOH

HDMI_CTRLDATA

R79 *2.21K_1%_04

SDVO/DP/iHDMI

Concurrent with PCIe

CLK_DREFSS# 2

R170

1K_1%_04

DMI_TXP2 23

MC H_CFG _16

MCH_NC_15

MCH_ICH_SYNC# 24

MCH_NC_11

MC H_CFG _12

C703

.01U_50V_X7R_04

MCH_CFG_11

Zdiff=

70O? 0%

MCH_BSEL12

DMI_TXP3 23

MCH_NC_18

CLK_DREF#

MCH_CFG_3

MCH_CFG_12

MCH_CFG_13

clock un-gating

MC H_HDA_SDO 22

MC H_CFG _7 MCH_RSVD16

CLK_DREF SS

R133 *0 _ 04 _ + U

CLK_DR EF# 2

MCH_CFG_8

D03-0221

1.8V

MCH_RSVD10

M_ CS3 # 1 3

MC H_CLKREQ #

3.3VS

FSB Dynamic ODT

DMI_TXN2 23

MC H_HD A_RST# 22

MCH_CFG_19

DMI X2 select Low= DMI x 2

High=DMI x 4 (default)

DMI lane reversal

MCH_NC_23

MCH_RSVD7

R109 2.2K_04

Add 0.1uF capacitor on this

rail close to (G)MCH.

DD R3_D RAMRST#

HDMI_CTRLDATA43

MCH_NC_21

SM_RCOMP_VOL

M_CLK_DD R0# 12

MCH_RSVD20

M_CLK_DD R1 12

CL_DATA0 24

PM_BMB USY#24

MC H_CFG _9

R77 *2.21K_1%_04

MCH_NC_26

Zo= 55O? 5%

CHANGE TO 33_04

Z0704

? ? ? ? DISABLE :0_04 TO ? ?

DMI_R XN1 23

PM

MISC

NC

DDR CLK/ CONTROL/COMPENSATIONCLK

DMI

CFG

RSVD

GRAPHICS VIDMEHDA

U23B

CAN TIGA

AP24

AT21

AV24

AR24

AR21

AU24

BC28

AY28

AY36

BB36

BA17

AY16

AV16

AR13

BC36

BD17

AY17

BF15

AY13

BG22

BH21

P29

R28

P25

T25

R25

T28

P20

P24

C25

N24

M2 4

E21

C23

C24

N21

P21

T21

R20

M2 0

L21

H21

R29

N33

P32

AT40

AT11

B38

A38

E41

F41

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

AL34

AN35

AK34

AM35

BG23

BF23

BH18

BF18

B7

AU20

AV20

AY21

AH9

AH10

AH12

AH13

M3 6

N36

R33

T33

B33

B32

G33

F33

C34

BF28

BH28

T20

R32

K12

AH37

AH36

AN36

AJ35

AH34

A47

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH6

BH5

BG4

G36

E36

K36

T24

H36

B12

E43

F43

BH3

E33

B31

N28

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

F1

AV42

AR36

BF17

M1

B28

B30

B29

C29

A28

M2 8

B2

SA_CK_0

SA_CK_1

SB_CK_0

SA_CK#_0

SA_CK#_1

SB_CK#_0

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SM_DRAMRST#

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_R COMP

SM_RCOMP#

CFG_18

CFG_19

CFG_2

CFG_0

CFG_1

CFG_20

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

PM_SYN C#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

D MI_RXN_0

D MI_RXN_1

D MI_RXN_2

D MI_RXN_3

DMI_R XP_0

DMI_R XP_1

DMI_R XP_2

DMI_R XP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

RSVD10

RSVD12

RSVD11

RSVD13

RSVD22

RSVD23

RSVD24

RSVD25

PM_DPR STP#

SB_CK_1

SB_CK#_1

RSVD20

RSVD5

RSVD6

RSVD7

RSVD8

RSVD1

RSVD2

RSVD3

RSVD4

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

SM_R CO MP_VOH

SM_RCOMP_VOL

TH ERMTRIP#

DPRSLPVR

RSVD9

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

NC_26

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

SDVO_CTRLCLK

SDVO_C TRLDATA

CLKR EQ#

RSVD14

IC H_SYN C#

TSATN#

PEG_CLK#

PEG_CLK

NC_16

GFX_VID_4

RSVD15

DDPC_CTRLCLK

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

SM_VR EF

SM_PWROK

SM_REXT

RSVD17

HD A_BCLK

HDA_RST#

HD A_SD I

HDA_SDO

HDA_SYNC

DDPC_CTRLDATA

RSVD16

1.05VS

MCH_NC_14

MC H_CFG _13

MCH_CFG_19

MCH_RSVD13

R129 *0 _ 04 _ + U

M_ CKE 2 13

R485 *20_1%_06

Zo=

55O? 5%

DMI_TXN0 23

CLK_DR EF 2

MCH_RSVD8

M_VREF _MCH

M_ CKE 1 12

DMI_R XN3 23

MC H_CFG _10

C706

2.2U _6.3V_06

1.05VS

MCH_NC_24

PM_EXTTS1#

M_ CKE 0 12

SM_RCOMP#

MCH_RSTIN#

SM_RCOMP_VOL

MCH_RSVD12

??3.3VS

Sheet 7 of 51

CANTIGA 3/7