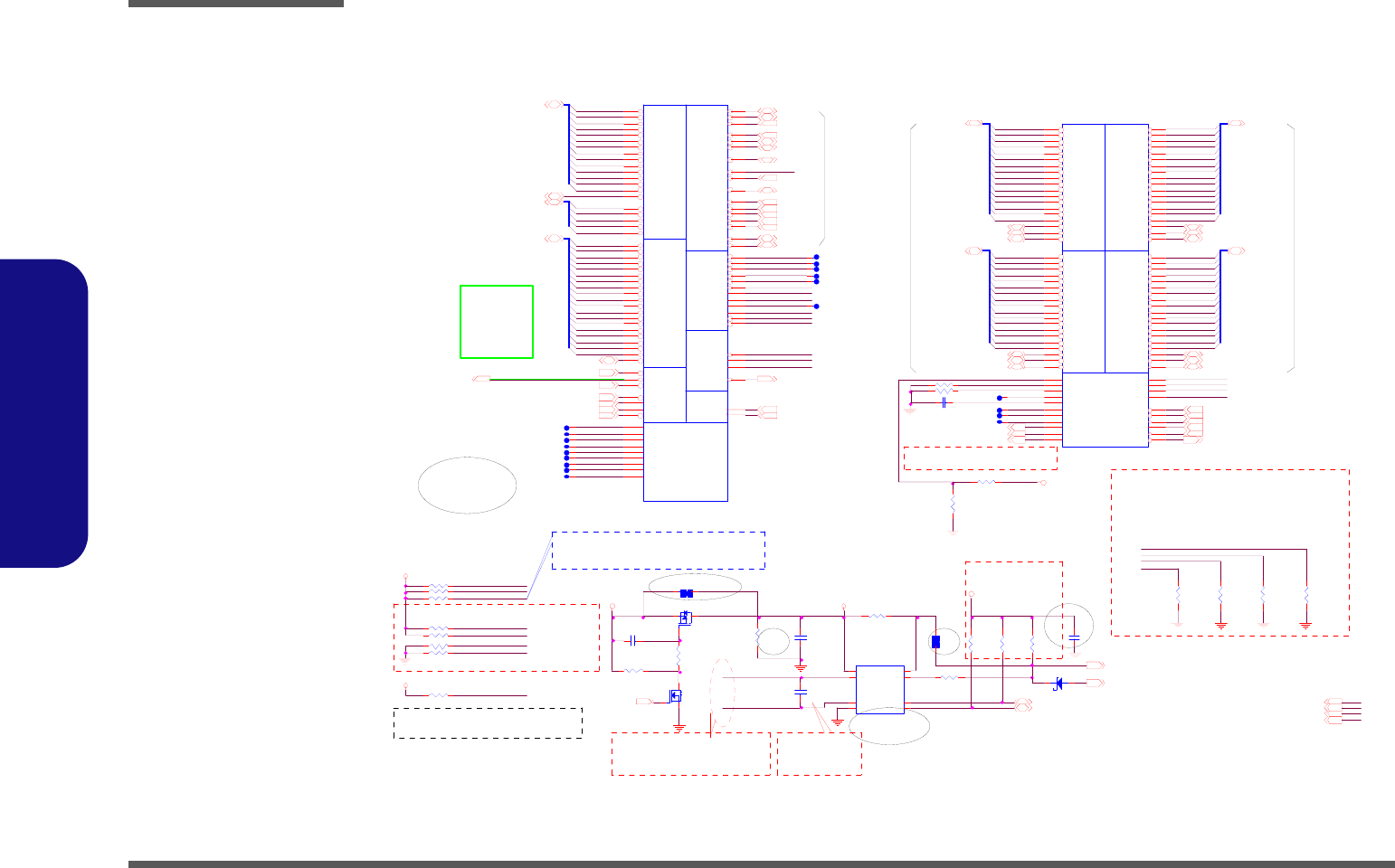

Schematic Diagrams

B - 4 Penryn (Socket-P) CPU 1/2

B.Schematic Diagrams

Penryn (Socket-P) CPU 1/2

Sheet 3 of 51

Penryn (Socket-P)

CPU 1/2

COMP0

H_D#50

SMC_CPU_THERM34

H_DSTBP#25

H_D#7

H_A#21

H_D#22

CPU_TEST5

C613 *.1U_10V_X7R_04

H_CPURST# 1"<L<5"

no decoupling should be

placed on the

GTLREF pin

H_REQ #[4:0]5

CPUR SVD06

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil spacing.

Layout Note:

R392 1K_1%_04

H_BR0#5

CLK_CPU_BCLK2

1.05VS2,4,5,7,9,10,22,25,37,39

H_TMS

H_D#52

D6 SCS751V-40

AC

Zo= 55O? 5%

D03B

R64

*100K_04

H_D#37

COMP3

H_A#28

H_R EQ#2

H_A#13

H_A#6

H_A#3

R70 *20mil_short

COMP[3:0]

traces should be at least 25 mils (> 50 mils

preferred) away from any other toggling

signal.

H_DIN V#05

C201

1U_6.3V_04

R29

27.4_1%_04

R87

*20K_04

H_D#51

H_D#26

C221

*.1U_16V_04

SMD_CPU_THERM34

H_PR EQ#

H_A#22

CPUR SVD04

R92

*100K_04

H_A#9

H_A#15

H_A#14

H_D#19

R60 56_04

H_N MI22

H_D#6

H_DIN V#15

CPU_TEST3

R67 *0_04

D03A-0313

H_A#[35:3]5

H_D#56

ADDR

GROUP_0

ADDR

GROUP_1

CONTROLXDP/ITP SIGNALS

H CL K

THERMAL

RESERVED

IC H

U22A

Penryn

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

D2

D22

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD4

AD3

AD1

AC4

G5

F1

C20

E1

H5

F21

A5

G6

E4

D20

C4

B3

C6

B4

H4

AC2

AC1

D21

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC5

AA 6

AB 3

C7

A24

B25

AB 5

G2

AB 6

W3

AA4

AB2

AA3

F6

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[3]#

A[30]#

A[31]#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

ADS#

ADSTB[0]#

ADSTB[1]#

RSVD[08]

BC LK[0]

BC LK[1]

BNR#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

BPRI#

BR0#

DBR #

DBSY#

DEFER#

DR DY #

FERR#

HIT#

HITM #

IERR #

IG NN E#

IN IT#

LINT0

LINT1

LOCK#

PRDY #

PREQ#

PRO CHO T#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

RESET#

RS[0]#

RS[1]#

RS[2]#

SMI#

STPC LK#

TCK

TDI

TD O

THERMTRIP#

TH ERM DA

THERMDC

TMS

TR DY #

TR ST#

A[32]#

A[33]#

A[34]#

A[35]#

RSVD[09]

R34 649_1%_06

H_D#38

H_D#61

H_A#[35:3]5

H_TDI

H_A#17

H_D#33

H_NMI

H_INTR

H_A20M#

H_DPSLP#

H_IGNNE#

H_INIT#

H_SMI#

H_STPCLK#

0.5" < L< 12"

CPU TO ICH with same

ground plane

H_TMS

CPUR SVD09

CPUR SVD02

R66

* 10m i l_shor t

R57 56_04

H_D#4

H_A#30

H_IN TR22

H_D#36

H_D#35

H_D#40

H_D#43

H_ADS# 5

H_D#47

H_HIT#5

H_A#23

H_A#7

Layout Note:

PSI#41

Layout Note:

THE RM_RST#34

D03-0221

H_DBSY# 5

H_CPURST#5

H_A20M#22

H_IG NNE#22

COMP1

H_A#35

H_R EQ#3

H_D#45

R397

27.4_1%_04

H_D#[63: 0] 5

H_D#62

H_TH ERMDA

H_D#17

CPU_TEST6

H_BPM1#

H_DSTBN #15

H_D#13

H_D#41

H_BPM2#

H_D#28

H_BPM0#

Layout note:

PM_TH RM# 24

CPU_BSE L02

H_BPM3#

D03-0221

1.05VS

H_INIT# 22

H_A#29

H_A#16

R74

*10K_04

H_BPRI# 5

H_A#25

H_D#24

COMP2CPU_TEST2

COMP2

COMP1

H_D#3

TO POWER PAGE

H_DEFER#5

COMP0

CPU_TEST4

H_D#39

CPUR SVD05

R30 54.9_1%_04

VDD3

1.05VS

H_D#32

D03-0221

H_DINV#2 5

THERM_ALERT# 34

H_D#10

Z0303

H_SM I#22

H_D#18

If PROCHOT# is routed between CPU, IMVP and MCH,

pull-up resistor has to be 68 ohm ? 5%. If not

use, pull-up resistor has to be 56 ohm ?5%

H_PWRGD <12" (CPU TO ICH9M)

H_ADS TB#05

Near to Thermal

IC

H_TRST#

H_DSTBN #05

H_D#54

3.3VS2,6,7,10,12,13,14,15,22,23,24,25,26,27,28,29,30,31,32,33,34,35,39,41,43

H_PRD Y#

COMP3

H_DSTBP#05

PM_TH RMTRIP# 7,22

H_D#27

H_A#34

H_PWRGD22

H_THER MDC

H_R EQ#1

H_THER MDA

<12inches

H_DSTBP#35

H_D#59

H_DSTBN#3 5

H_D#55

H_D#49

H_R EQ#4

H_DPSLP# 22

H_D#58

H_PREQ#

H_TRDY#5

H_A#18

H_D#21

CPU_BSE L22

Z0302

H_IERR #

R394

2K_1%_04

H_HITM# 5

CPU_BSE L12

CPU_TEST1

H_D#46

H_PRO CH OT#

H_D#25

H_FERR#22

H_CPUSLP#5

H_D#14

3.3V

H_PROC HOT#

H_D#30

R69

4.7K_04

H_LOCK#5

H_D#44

10mils

H_A#8

H_D#[63:0]5

ITP_DBR ST#

Z0306

R65

10K_04

H_D#48

C225

*.01U_16V_04

H_RS#25

H_D#16

CPUR SVD03

H_DINV#3 5

H_DPWR#5

R395

54.9_1%_04

H_A#31

Zo= 55O? 5%

H_D#[63: 0] 5

H_DPRSTP# 7,22,41

H_TRST#

H_D#34

H_D#15

H_D#60

H_D#1

D03-0221

H_D#8

H_D#[63:0]5

VDD322,34,35,36,40

H_A#11

H_D#23

R33 54.9_1%_04

H_A#4

H_TDI

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms

COMP1, COMP3: 0.5" Max, Zo=55 Ohms

Best estimate is 18 mils wide trace for outer

layers and 14 mils wide trace if on internal

layers.

H_D#29

H_TCK

H_D#9

H_AD STB#15

Within 2.0"

of the CPU

H_D#5

H_D#57

CPUR SVD01

H_DSTBP#15

H_D#31

H _B NR# 5

H_A#19

Z0307

H_A#10

Zo= 55O? 5%

CPU_TEST7

R56 *1K_04

H_STPCLK#22

H_A#12

H_A#5

H_R EQ#0

H_A#27

H_D#20

H_DSTBN#2 5

NEAR EC

CPUR SVD08

H_A#20

CPUR SVD07

Q3

*AO 340 9

G

DS

DATA GR P 0 DATA GR P 1

DAT A GRP 2DATA GRP 3

MISC

U22B

Penryn

R26

U26

AA1

Y1

E22

F24

J24

J23

H22

F26

K22

H23

N22

K25

P26

R23

E26

L23

M2 4

L22

M2 3

P25

P23

P22

T24

R24

L25

G22

T25

N25

Y22

AB24

V24

V26

V23

T22

U25

U23

F23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

AE24

AD24

G25

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

E25

AC22

AD23

AF22

AC23

E23

K24

G24

AF1

H25

N24

U22

AC20

E5

B5

D24

J26

L26

Y26

AE25

H26

M2 6

AA26

AF24

AD26

AE6

D6

D7

C24

B22

B23

C21

D25

AF26

A26

C23

C3

CO MP[0]

CO MP[1]

CO MP[2]

CO MP[3]

D[0]#

D[1]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

D[16]#

D[17]#

D[18]#

D[19]#

D[2]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[3]#

D[30]#

D[31]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[4]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[5]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[6]#

D[60]#

D[61]#

D[62]#

D[63]#

D[7]#

D[8]#

D[9]#

TEST5

DIN V[0]#

DIN V[1]#

DINV[2]#

DINV[3]#

DPRSTP#

DPSLP#

DPWR#

DSTBN [0]#

DSTBN [1]#

DSTBN[2]#

DSTBN[3]#

DSTBP[0]#

DSTBP[1]#

DSTBP[2]#

DSTBP[3]#

GTLREF

PSI#

PWRGOOD

SLP#

TEST3

BSEL[0]

BSEL[1]

BSEL[2]

TEST2

TEST4

TEST6

TEST1

TEST7

H_DRDY# 5

H_D#11

H_D#2

V_THRM

H_RS#15

H_IERR#

R31 54.9_1%_04

H_A#33

H_A#32

H_D#63

U6

W83L771AWG

1

2

3

4

5

6

7

8

VDD

D+

D-

THERM

GND

ALER T

SDATA

SC LK

Layout note:

Zo=55 ohm, 0.5"max for GTLREF

ITP _D BRST#

C198

1000P_50V_04

H_A#24

H_TH ERMDC

H_TCK

R28

54.9_1%_04

R68

4.7K_04

H_D#42

H_TDO

CPU_GTLREF

H_D#53

CLK_CPU_BCLK# 2

R62 *1K_04

R32 54.9_1%_04

DESIGN GUIDE P.65

THERMAL SENSER

H_TDI

Circult: 54.9 ohm check 150 ohm

H_RS#05

H_D#0

H_A#26

H_D#12

3.3VS

3.3V14,15,22,23,24,25,26,28,30,31,35,37,38

R416 *1K_04

Q6

*2 N7 0 02 W

G

DS