DIGITAL-LOGIC AG SMA200 Manual V1.0

27

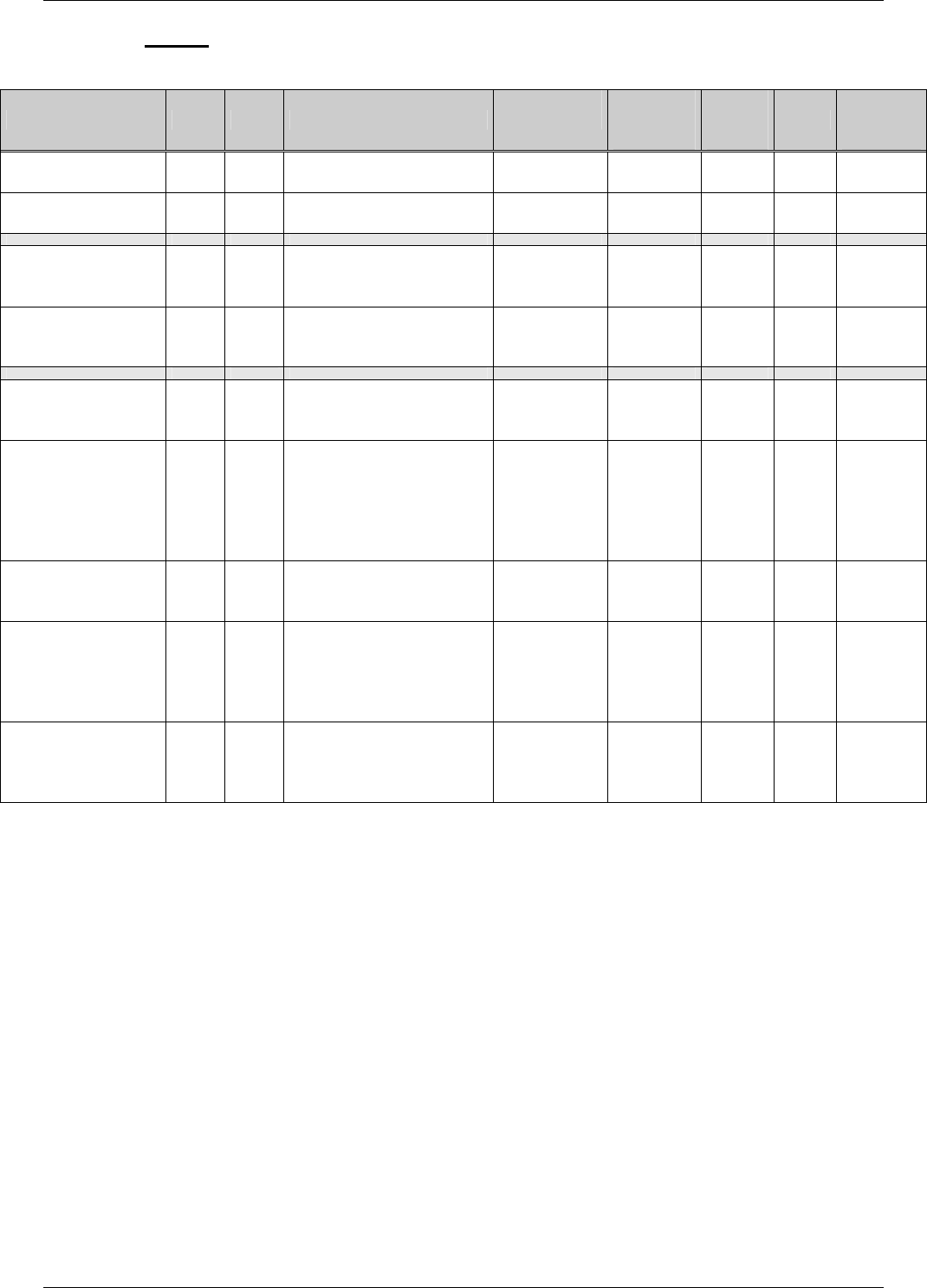

5.4.3. LVDS

Signal BUS Type Description

On Module

Termination

Ext. Ter-

mination

Needed

Max.

Length

in mm

Ohm

Matched

Length in

mm

LVDS_DDCCLK LVDS

3.3V DDC signal PU 10k to

3.3V

- 150 55

LVDS_DDCDAT LVDS

3.3V DDC signal PU 10k to

3.3V

- 150 55

LVDS_DATA[0..3] +/-

LVDS

Dif

Out

LVDS data signal

Connected directly to the

display.

- - 150 100 0.5

LVDS_CLK +/- LVDS

Dif

Out

LVDS clock signal

Connected directly

to the

display.

- - 150 100 0.5

LVDS_VDDEN LVDS

3.3V

Out

LVDS control signal

To switch on/off the VDD

of the LVDS display.

100k pull

down

- 150 55

LVDS_BKLCTL LVDS

3.3V

Out

Connected to the LVDS

display’s PWM-based

backlight inverter

module. No multi-bus

master mode is

supported.

- 150 55

LVDS_BKLEN LVDS

3.3V

Out

Connected to the LVDS

display’s backlight

inverter module switch.

100k pull

down

- 150 55

LVDS_CTLA_CLK LVDS

3.3V

I/O

Connected to the LVDS

display’s PWM-based

backlight inverter

module. No multi bus

master mode supported.

PU 4.7k to

3.3V

- 150 55

LVDS_CTLB_DATA

LVDS

3.3V

I/O

Connected to the LVDS

display’s PWM-based

backlight inverter

module.

PU 4.7k to

3.3V

- 150 55

If the signals are not used:

All these LVDS signals may be left open.

Remarks:

For the DDC signals, a voltage translator to 3.3V or 5V is needed.

Pair to Pair spacing: 35mil = 0.9mm

Pair to Pair matching: better than 25mm

Bus to Bus spacing: 20mil = 0.5mm

Maximum via count: 0 2.

EMV/EMI filters: