+RVW6RIWZDUH3URFHVVHG9.IOH[

0RGHP'HYLFH)DPLO\IRU'HVNWRS$SSOLFDWLRQV 6RIW.3&,

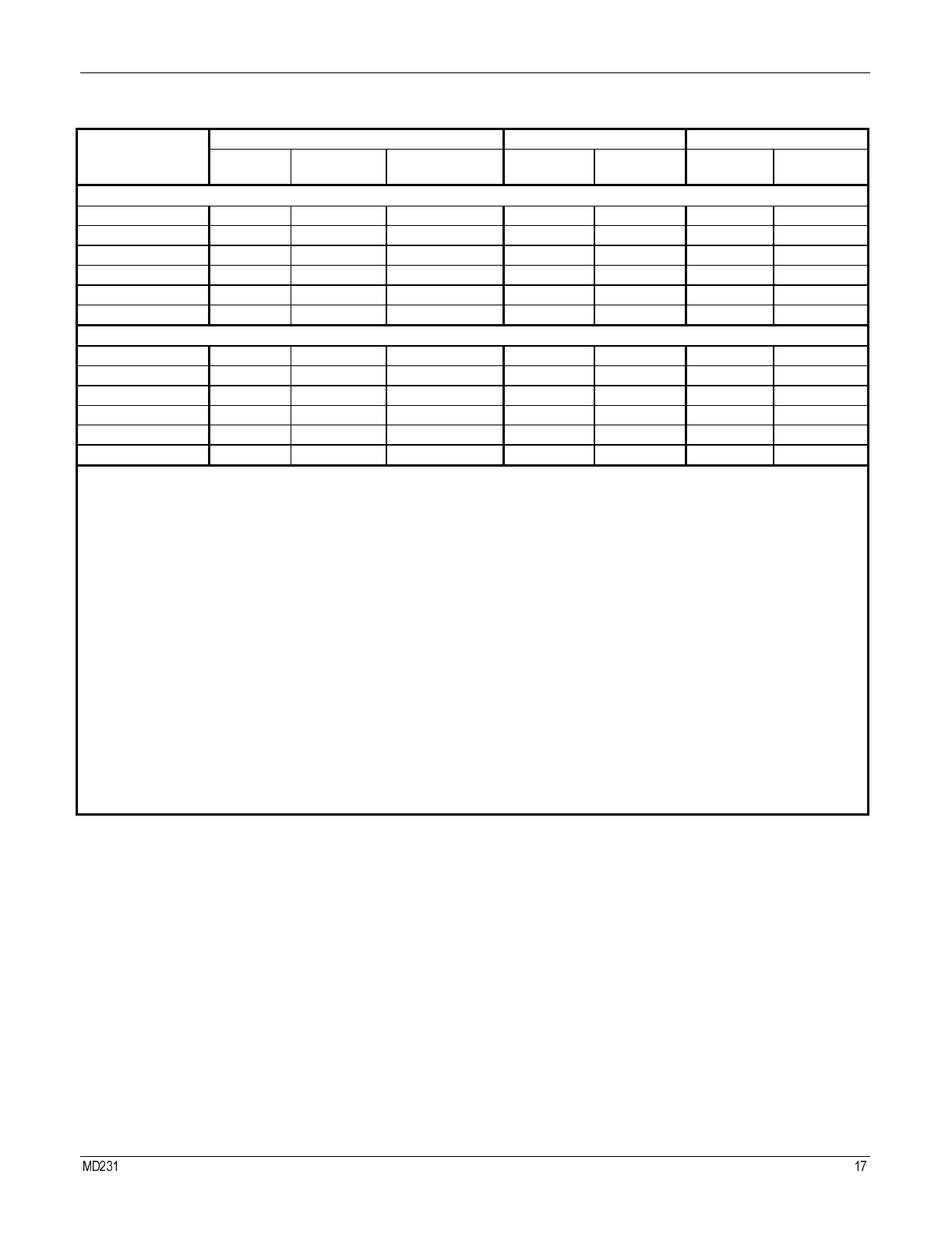

Table 2. Current and Power Requirements

Conditions Current Power

Device State (Dx)

and Bus State (Bx)

PCI Bus

Power

PCI Clock

(PCICLK)

Line

Connection

Typical

Current (mA)

Maximum

Current (mA)

Typical

Power (mW)

Maximum

Power (mW)

Single Device (R6793-12 BIC) and 2-Device Set (11235-14 BIF and 20437-11 LC)

D0, B0 On Running Yes 33 36 109 130

D0, B0 On Running No 22 24 73 86

D3, B0 On Running No 22 24 73 86

D3, B1 On Running No 22 24 73 86

D3, B2, B3 (D3 hot) On Stopped No 2.1 3.2 6.9 11.5

D3, B3 (D3 cold) Off Stopped No <1 1 <3.3 3.6

Single Device (R6793-11 BIC) and 2-Device Set (11235-14 BIF and 20410-11 LVC)

D0, B0 On Running Yes 33 36 109 130

D0, B0 On Running No 22 24 73 86

D3, B0 On Running No 22 24 73 86

D3, B1 On Running No 22 24 73 86

D3, B2, B3 (D3 hot) On Stopped No 2.1 3.2 6.9 11.5

D3, B3 (D3 cold) Off Stopped No <1 1 <3.3 3.6

Notes:

Operating voltage: VDD = +3.3V ± 0.3V.

Test conditions: VDD = +3.3 VDC for typical values; VDD = +3.6 VDC for maximum values.

For all modes, +3.3V is supplied to BIF and LVC and LC.

Definitions:

PCI Bus Power On: PCI Bus +5V and +3.3V on (modem normally powered by +3.3V from PCI Bus +3.3V

or regulated down from PCI Bus +5V); PCI RST# not asserted.

Off: PCI Bus +5V and +3.3V off (modem normally powered by +3.3V from Vaux or Vpci); PCI RST# asserted.

PCI Clock (PCICLK) Running: PCI Bus signal PCICLK running;

Stopped: PCI Bus signal PCICLK stopped (off).

Line connection: Yes: Off-hook, IA powered.

No: On-hook, IA powered down.

Device States: D3: Low power state. Suspend state can change the system power state; the resulting power state depends

on the system architecture (OS, BIOS, hardware) and system configuration (i.e., other PCI installed cards).

D0: Full power state.

Device and Bus States: D0, B0: Any PCI transaction, PCICLK running, VCC present.

D3, B1: No PCI Bus transactions, PCICLK running, VCC present.

D3, B2, B3: No PCI transactions, PCICLK stopped, VCC may be present.

D3, B3: No PCI transactions, PCICLK stopped, no VCC.

Refer to the PCI Bus Power Management Interface Specification for additional information.