CY7C185

Document #: 38-05043 Rev. *A Page 6 of 11

Notes:

15. The minimum write cycle time for write cycle #3 (WE

controlled, OE LOW) is the sum of t

HZWE

and t

SD

.

16. If CE

1

goes HIGH or CE

2

goes LOW simultaneously with WE HIGH, the output remains in a high-impedance state.

Switching Waveforms (continued)

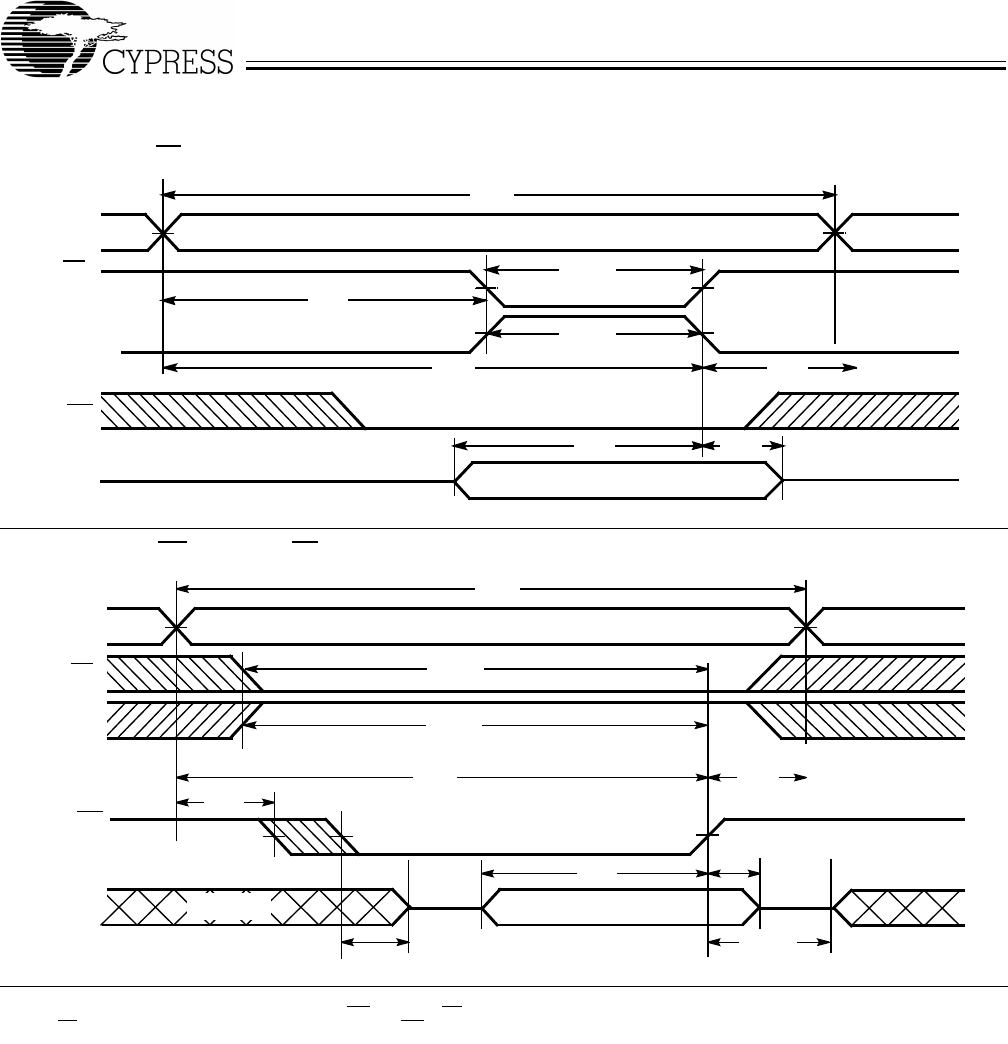

t

WC

t

AW

t

SA

t

HA

t

HD

t

SD

t

SCE1

WE

DATA I/O

ADDRESS

CE

1

DATA

IN

VALID

t

SCE2

CE

2

rite Cycle No. 2 (CE Controlled)

[13,14,15]

t

HD

t

SD

t

LZWE

t

SA

t

HA

t

AW

t

WC

t

HZWE

DATA

IN

VALID

t

SCE1

t

SCE2

CE

1

CE

2

ADDRESS

DATA I/O

WE

Write Cycle No. 3 (WE Controlled, OE LOW)

[13,14,15,16]

NOTE 14