AN46860

December 12, 2008 Document No. 001-46860 Rev. *A 3

Clocks

1. Ensure that the XTALSLC[1:0] pin levels correspond to

the frequency of the signal at XTALIN and XTALOUT.

2. Leave the XTALOUT floating if an external clock source

is used.

3. Clock or crystal characteristics must conform to the

requirements specified in the data sheet.

4. The design must adhere to the power supply noise

specifications for the PLL specified in the data sheet.

5. XVDDQ is the select pin for crystal and clock. XVDDQ

must be 3.3V when using a crystal. XVDDQ must be

1.8V when using a clock source as an input.

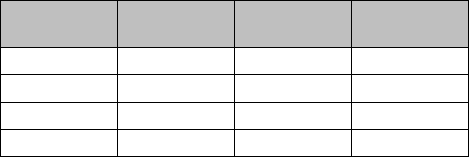

Table 5 lists the various clock selection input settings.

Table 5. Clock Selection Input Settings

XTALSLC[1]

XTALSLC[0]

Clock

Frequency

Crystal

Support

0

0

19.2 MHz

Yes

0

1

24 MHz

Yes

1

0

48 MHz

No

1

1

26 MHz

Yes

Decoupling for Power Supplies

1. VDD requires 2.2 µF and 0.1 µF decoupling.

2. Although AVDDQ is tied to the same supply as VDD,

route it separately with 0.01 µF and 0.1 µF capacitors.

3. UVDDQ requires 2.2 µF and 0.1 µF decoupling.

4. GVDDQ, PVDDQ, SSVDDQ, SNVDDQ, and XVDDQ

do not have any specific decoupling requirements.

Combine them with the decoupling for other supplies at

the same level. If in doubt, use 2.2 µF and 0.1 µF.

Miscellaneous

All unused output-only pins may be left floating, but do not

leave unused input-only and input/output pins floating. Tie

the unused input-only and input/output to a valid logic level

using a single 10k pull up resistor. There is a negligible

difference if the unused input-only pins are tied HIGH or

LOW. For lowest leakage, tie unused input/output pins

HIGH.

Ensure that all unused pins handled in this manner are tied

to their corresponding power domain. For example, an

unused GPIO[1] is tied HIGH to GVDDQ through a 10k pull

up, which is shared with other unused signals in the GVDDQ

power domain.

Astoria is not hardware backward compatible to Antioch. So,

if the system is designed in Antioch, it requires PCB change

when replaced by Astoria.

About the Author

Name:

Praveen Kumar

Title:

Applications Engineer

Contact:

prku@cypress.com.

5B

[+] Feedback