February 19, 2008 Document No. 001-15342 Rev. ** 4

AN6077

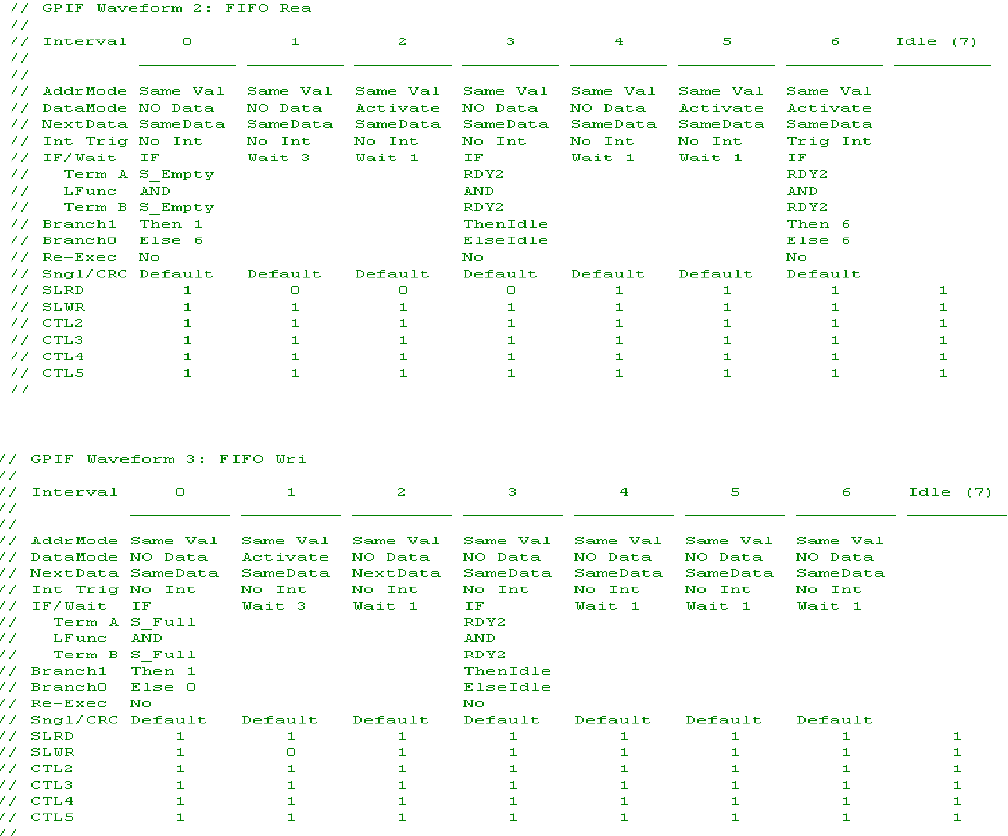

Figure 4. FIFO Read Waveform in gpif.c

Figure 5. FIFO Write Waveform in gpif.c

8051 Firmware Programming (Master)

This section describes how to configure the 8051 to support

the interface on the master side (register settings and others)

and discusses the firmware implemented to perform data

transactions over the local bus and the USB. The complete

code listing is provided at the end of this document.

Firmware Architecture

The firmware is designed to handle USB INs and OUTs arbi-

trarily (for example, the direction of transfer is not favored).

It is also fairly deterministic in its approach and is ‘event-

driven’ by the following key conditions:

OUTs (FIFO Writes)

■ Endpoint 2 OUT Has Data

■ Peripheral Interface Not Busy (GPIF IDLE)

■ Slave Interface FIFO Not Full

INs (FIFO Reads)

■ Peripheral Interface Not Busy (GPIF IDLE)

■ Slave Interface FIFO Not Empty

■ Endpoint 6IN Available Not Full

Since the GPIF is a shared resource between FIFO Reads

and Writes, the peripheral interface status is always checked

before committing the GPIF to launch any form of physical

bus transactions. The firmware is optimized for 512-byte

FIFO Reads and Writes with other mechanisms in place to

handle short packets (1–511 bytes).

[+] Feedback