CY25566

Document #: 38-07429 Rev. *B Page 7 of 9

Absolute Maximum Ratings

[1, 2]

Supply Voltage (V

DD

: .......................................................+6V

Operating Temperature:......................................0°C to 70°C

Storage Temperature ..................................–65°C to +150°C

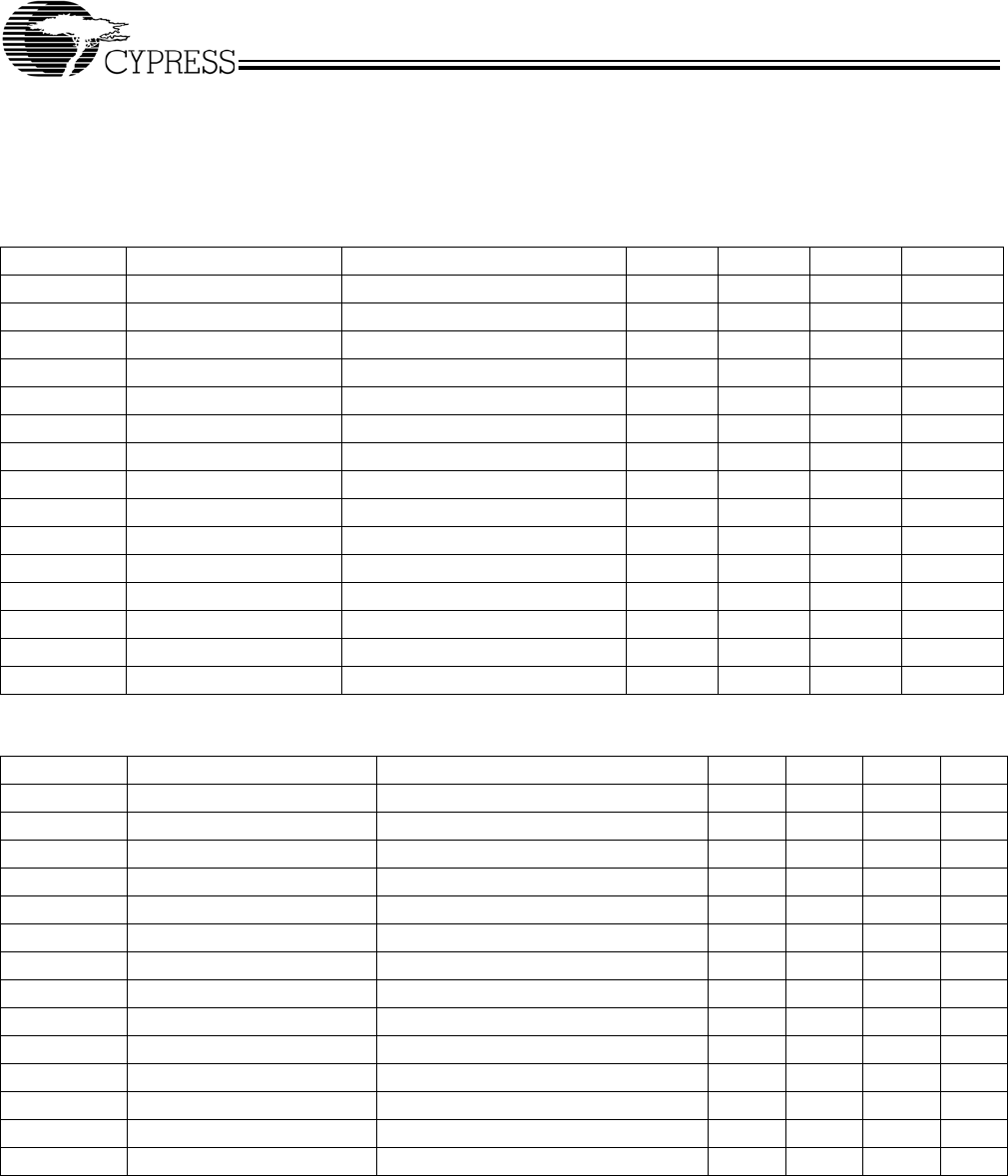

Table 4. DC Electrical Characteristics V

DD

= 3.3V, Temp. = 25°C, unless otherwise noted

Parameter Description Conditions Min. Typ. Max. Unit

V

DD

Power Supply Range ±10% 2.97 3.3 3.63 V

V

INH

Input High Voltage S0 and S1 only. 0.85V

DD

V

DD

V

DD

V

V

INM

Input Middle Voltage S0 and S1 only. 0.40V

DD

0.50V

DD

0.60V

DD

V

V

INL

Input Low Voltage S0 and S1 only. 0.0 0.0 0.15V

DD

V

V

OH1

Output High Voltage I

OH

= 6 ma, SSCLKa 2.4 V

V

OH2

Output High Voltage I

OH

= 20 ma, SSCLKb 2.0 V

V

OL1

Output Low Voltage I

OH

= 6 ma, SSCLKa 0.4 V

V

OL2

Output Low Voltage I

OH

= 20 ma, SSCLKb 1.2 V

C

in1

Input Capacitance Xin/CLK (Pin 1) 3 4 5 pF

C

in2

Input Capacitance Xout (Pin 8) 6 8 10 pF

C

in2

Input Capacitance All input pins except 1. 3 4 5 pF

I

DD1

Power Supply Current FIN = 40 MHz,15 pF@all outputs 27 32 mA

I

DD1

Power Supply Current FIN = 40 MHz, No Load 21 28 mA

I

DD2

Power Supply Current FIN = 165 MHz,15 pF@all outputs 68 80 mA

I

DD2

Power Supply Current FIN = 165 MHz, No Load 48 60 mA

Table 5. Electrical Timing Characteristics V

DD

= 3.3V, T = 25°C and C

L

= 15 pF, unless otherwise noted. Rise/Fall @ 0.4–2.4V,

Duty@1.5V

Parameter Description Conditions Min. Typ. Max Unit

I

CLKFR

Input Clock Frequency Range Non-crystal, 3.0V Pk–Pk ext. source 25 200 MHz

t

RISE(a)

Clock Rise Time SSCLK1a or SSCLK1b, Freq = 100 MHz 1.0 1.3 1.6 ns

t

FALL(a)

Clock Fall Time SSCLK1a or SSCLK1b, Freq = 100 MHz 1.0 1.3 1.6 ns

t

RISE(a+b)

Clock Rise Time SSCLK1(a+b), CL = 33 pF, 100 MHz 1.2 1.5 1.8 ns

t

FALL(a+b)

Clock Fall Time SSCLK1(a+b), CL = 33 pF, 100 MHz 1.2 1.5 1.8 ns

t

RISE(a+b)

Clock Rise Time SSCLK1(a+b), CL = 33 pF, 200 MHz 1.1 1.4 1.7 ns

t

FALL(a+b)

Clock Fall Time SSCLK1(a+b), CL = 33 pF, 200 MHz 1.1 1.4 1.7 ns

t

RISE(REF)

Clock Rise Time REFOUT, Pin 3, CL = 15 pF, 50 MHz 1.0 1.3 1.6 ns

t

FALL(REF)

Clock Fall Time REFOUT, Pin 3, CL = 15 pF, 50 MHz 1.0 1.3 1.6 ns

D

TYin

Input Clock Duty Cycle XIN/CLK (Pin) 30 50 70 %

D

TYout

Output Clock Duty Cycle SSCLK1a/b (Pin 8 and 9) 45 50 55 %

C

CJ1

Cycle-to-Cycle Jitter F = 100 MHz, SSCLK1a/b CL = 33 pF 300 400 ps

C

CJ2

Cycle-to-Cycle Jitter F = 200 MHz, SSCLK1a/b CL = 33 pF 500 600 ps

REFOUT Refout Frequency Range CL = 15 pF 25 108 MHz

Note:

1. Operation at any Absolute Maximum Rating is not implied.

2. Single Power Supply: The voltage on any input or I/O pin cannot exceed the power pin during power-up.

[+] Feedback