CY7B991

CY7B992

Document Number: 38-07138 Rev. *B Page 6 of 19

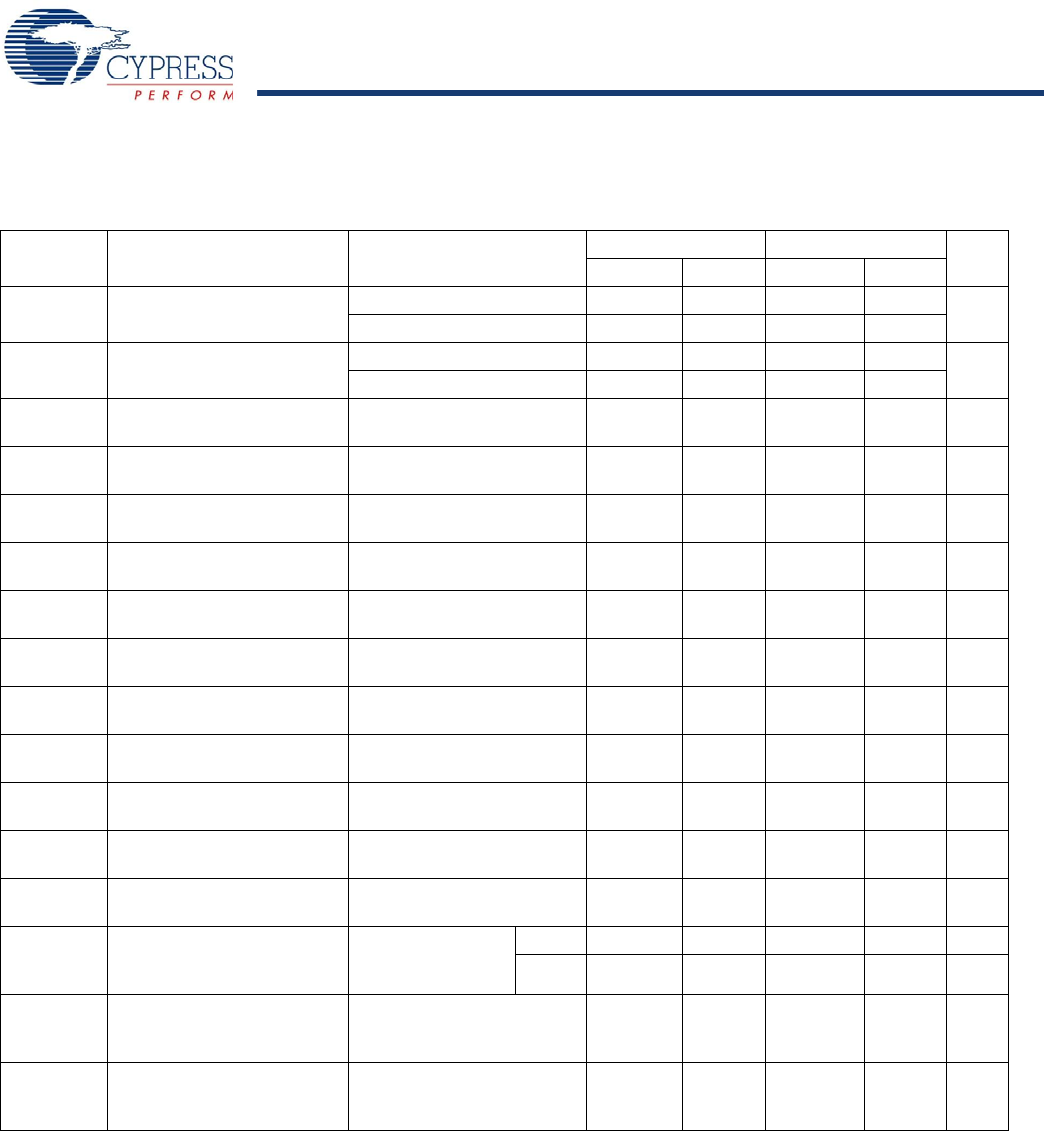

Electrical Characteristics

Over the Operating Range

[6]

CY7B991 CY7B992

Parameter Description Test Conditions Min Max Min Max Unit

V

OH

Output HIGH Voltage V

CC

= Min I

OH

= –16 mA 2.4 V

V

CC

= Min, I

OH

=–40 mA V

CC

–0.75

V

OL

Output LOW Voltage V

CC

= Min, I

OL

= 46 mA 0.45 V

V

CC

= Min, I

OL

= 46 mA 0.45

V

IH

Input HIGH Voltage

(REF and FB inputs only)

2.0 V

CC

V

CC

–

1.35

V

CC

V

V

IL

Input LOW Voltage

(REF and FB inputs only)

–0.5 0.8 –0.5 1.35 V

V

IHH

Three Level Input HIGH

Voltage (Test, FS, xFn)

[10]

Min ≤ V

CC

≤ Max V

CC

– 0.85 V

CC

V

CC

– 0.85 V

CC

V

V

IMM

Three Level Input MID

Voltage (Test, FS, xFn)

[10]

Min ≤ V

CC

≤ Max V

CC

/2 –

500 mV

V

CC

/2 +

500 mV

V

CC

/2 –

500 mV

V

CC

/2 +

500 mV

V

V

ILL

Three Level Input LOW

Voltage (Test, FS, xFn)

[10]

Min ≤ V

CC

≤

Maximum

0.0 0.85 0.0 0.85 V

I

IH

Input HIGH Leakage Current

(REF and FB inputs only)

V

CC

= Max, V

IN

= Max. 10 10 μA

I

IL

Input LOW Leakage Current

(REF and FB inputs only)

V

CC

= Max, V

IN

= 0.4V –500 –500 μA

I

IHH

Input HIGH Current

(Test, FS, xFn)

V

IN

= V

CC

200 200 μA

I

IMM

Input MID Current

(Test, FS, xFn)

V

IN

= V

CC

/2 –50 50 –50 50 μA

I

ILL

Input LOW Current

(Test, FS, xFn)

V

IN

= GND –200 –200 μA

I

OS

Output Short Circuit

Current

[8]

V

CC

= Max, V

OUT

= GND (25

°C only)

–250 N/A mA

I

CCQ

Operating Current Used by

Internal Circuitry

V

CCN

= V

CCQ

= Max,

All Input

Selects Open

Com’l 85 85 mA

Mil/Ind 90 90

I

CCN

Output Buffer Current per

Output Pair

[9]

V

CCN

= V

CCQ

= Max,

I

OUT

= 0 mA

Input Selects Open, f

MAX

14 19 mA

PD Power Dissipation per

Output Pair

[10]

V

CCN

= V

CCQ

= Max,

I

OUT

= 0 mA

Input Selects Open, f

MAX

78 104

[11]

mW

Notes

6. For more information see “Group A Subgroup Testing” on page 17.

7. These inputs are normally wired to V

CC

, GND, or left unconnected (actual threshold voltages vary as a percentage of V

CC

). Internal termination resistors hold

unconnected inputs at V

CC

/2. If these inputs are switched, the function and timing of the outputs may glitch and the PLL may require an additional t

LOCK

time before

all datasheet limits are achieved.

8. CY7B991 must be tested one output at a time, output shorted for less than one second, less than 10% duty cycle. Room temperature only. CY7B992 outputs must

not be shorted to GND. Doing so may cause permanent damage.

9. Total output current per output pairis approximated by the following expression that includes device current plus load current:

CY7B991: I

CCN

= [(4 + 0.11F) + [((835 – 3F)/Z) + (.0022FC)]N] x 1.1

CY7B992: I

CCN

= [(3.5+ 0.17F) + [((1160 – 2.8F)/Z) + (.0025FC)]N] x 1.1

Where

F = frequency in MHz; C = capacitive load in pF; Z = line impedance in ohms; N = number of loaded outputs; 0, 1, or 2; FC = F < C.

10.Total power dissipation per output pair can be approximated by the following expression that includes device power dissipation plus power dissipation due to the load

circuit:

CY7B991:PD = [(22 + 0.61F) + [((1550 – 2.7F)/Z) + (.0125FC)]N] x 1.1

CY7B992:PD = [(19.25+ 0.94F) + [((700 + 6F)/Z) + (.017FC)]N] x 1.1

See note 9 for variable definition.

11.Applies to REF and FB inputs only. Tested initially and after any design or process changes that may affect these parameters.

[+] Feedback