CY7C027V/027VN/027AV/028V

CY7C037V/037AV/038V

Document #: 38-06078 Rev. *B Page 14 of 18

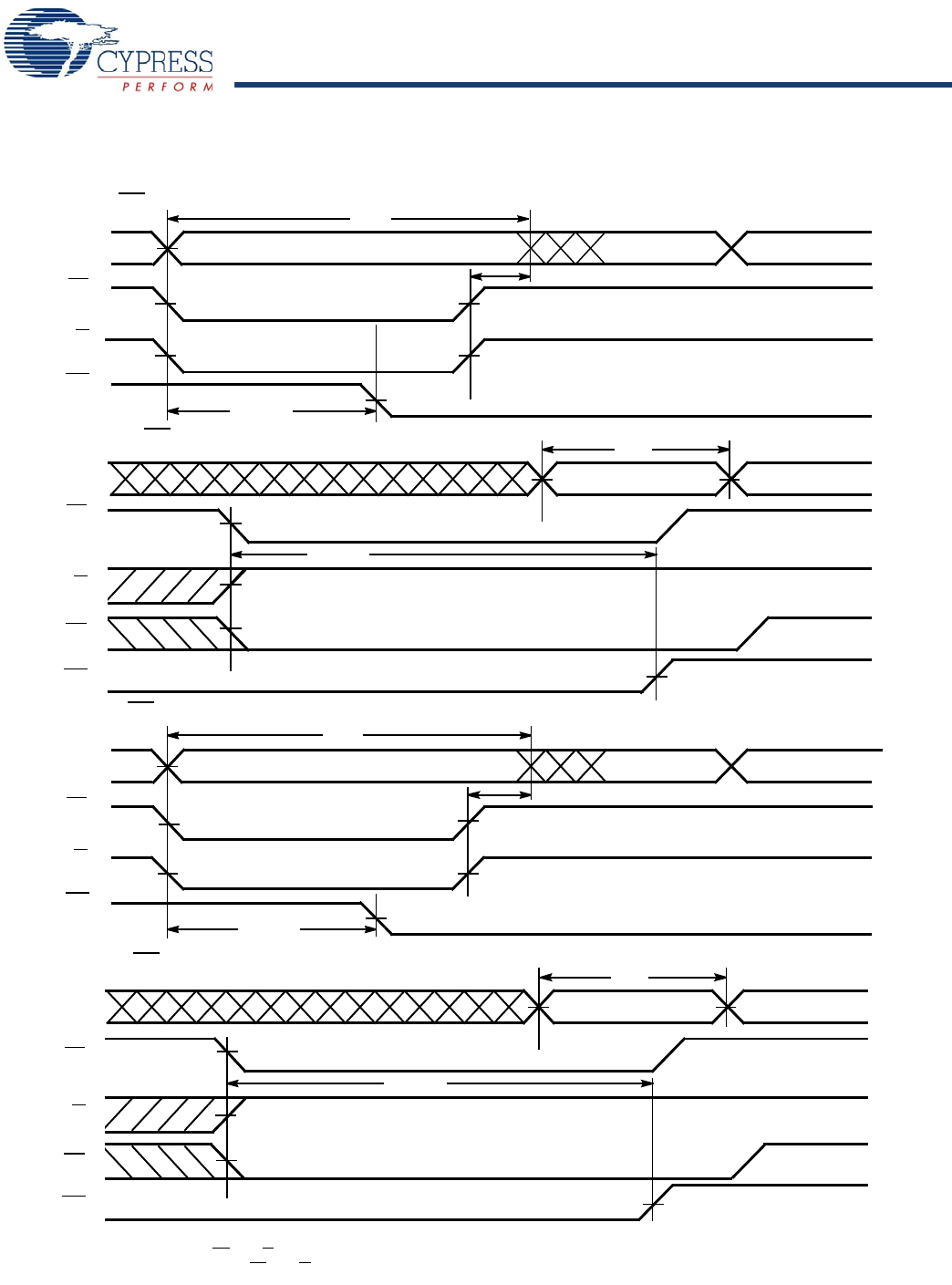

Figure 15. Interrupt Timing Diagrams

Notes

35.t

HA

depends on which enable pin (CE

L

or R/W

L

) is deasserted first.

36.t

INS

or t

INR

depends on which enable pin (CE

L

or R/W

L

) is asserted last.

Switching Waveforms

(continued)

WRITE 7FFF (FFFF for CY7C028V/38V)

t

WC

Right SideClears INT

R

:

t

HA

READ 7FFF

t

RC

t

INR

WRITE 7FFE (FFFE for CY7C028V/38V)

t

WC

Right SideSets INT

L

:

Left Side Sets INT

R

:

Left SideClears INT

L

:

READ 7FFE

t

INR

t

RC

ADDRESS

R

CE

L

R/W

L

INT

L

OE

L

ADDRESS

R

R/W

R

CE

R

INT

L

ADDRESS

R

CE

R

R/W

R

INT

R

OE

R

ADDRESS

L

R/W

L

CE

L

INT

R

t

INS

t

HA

t

INS

(FFFF for CY7C028V/38V)

(FFFF for CY7C028V/38V)

[35]

[36]

[36]

[36]

[35]

[36]

[+] Feedback