CY7C1316BV18, CY7C1916BV18

CY7C1318BV18, CY7C1320BV18

Document Number: 38-05621 Rev. *D Page 24 of 31

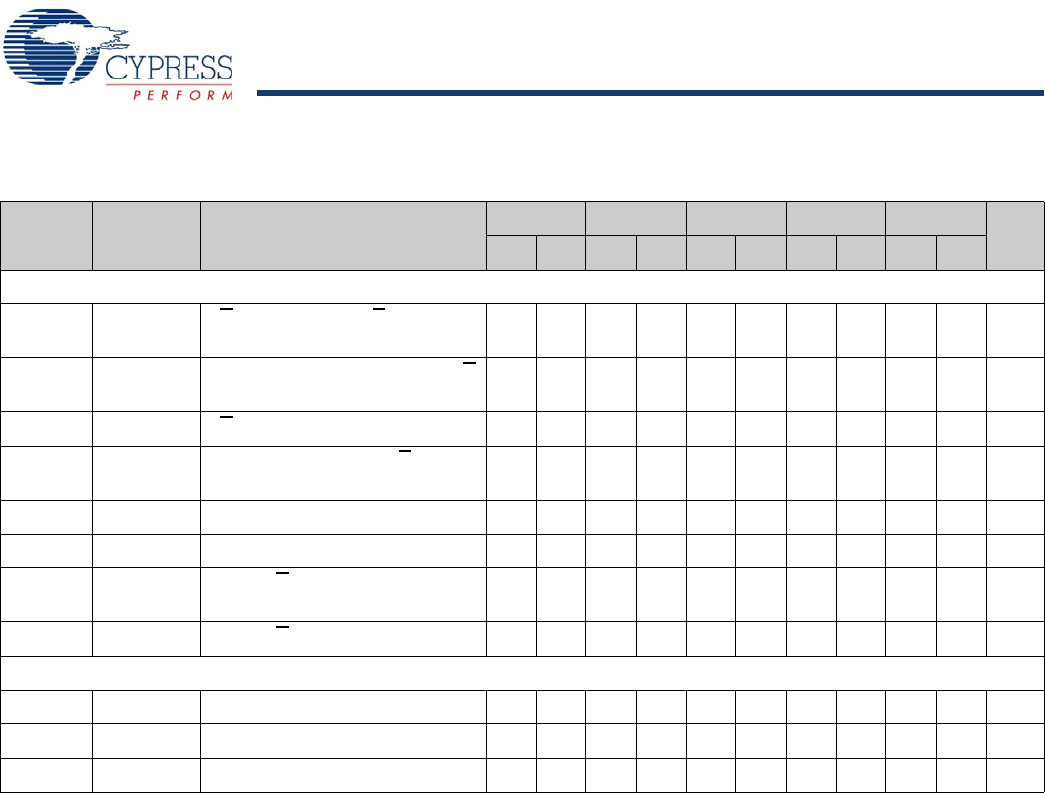

Output Times

t

CO

t

CHQV

C/C Clock Rise (or K/K in single

clock mode) to Data Valid

– 0.45 – 0.45 – 0.45 – 0.45 – 0.50 ns

t

DOH

t

CHQX

Data Output Hold after Output C/C

Clock Rise (Active to Active)

–0.45 – –0.45 – –0.45 – –0.45 – –0.50 – ns

t

CCQO

t

CHCQV

C/C Clock Rise to Echo Clock Valid – 0.45 – 0.45 – 0.45 – 0.45 – 0.50 ns

t

CQOH

t

CHCQX

Echo Clock Hold after C/C Clock

Rise

–0.45 – –0.45 – –0.45 – –0.45 – –0.50 – ns

t

CQD

t

CQHQV

Echo Clock High to Data Valid – 0.27 – 0.27 – 0.30 – 0.35 – 0.40 ns

t

CQDOH

t

CQHQX

Echo Clock High to Data Invalid –0.27 – –0.27 – –0.30 – –0.35 – –0.40 – ns

t

CHZ

t

CHQZ

Clock (C/C) Rise to High-Z

(Active to High-Z)

[24, 25]

– 0.45 – 0.45 – 0.45 – 0.45 – 0.50 ns

t

CLZ

t

CHQX1

Clock (C/C) Rise to Low-Z

[24, 25]

–0.45 – –0.45 – –0.45 – –0.45 – –0.50 – ns

DLL Timing

t

KC Var

t

KC Var

Clock Phase Jitter – 0.20 – 0.20 – 0.20 – 0.20 – 0.20 ns

t

KC lock

t

KC lock

DLL Lock Time (K, C) 1024 – 1024 – 1024 – 1024 – 1024 – Cycles

t

KC Reset

t

KC Reset

K Static to DLL Reset 30–30–30–30–30– ns

Switching Characteristics (continued)

Over the Operating Range

[20, 21]

Cypress

Parameter

Consortium

Parameter

Description

300 MHz 278 MHz 250 MHz 200 MHz 167 MHz

Unit

Min Max Min Max Min Max Min Max Min Max

Notes

24.t

CHZ

, t

CLZ

are specified with a load capacitance of 5 pF as in (b) of AC Test Loads and Waveforms on page 22. Transition is measured ±100 mV from steady-state voltage.

25.At any voltage and temperature t

CHZ

is less than t

CLZ

and t

CHZ

less than t

CO

.

[+] Feedback