CY7C1317CV18, CY7C1917CV18

CY7C1319CV18, CY7C1321CV18

Document Number: 001-07161 Rev. *D Page 25 of 31

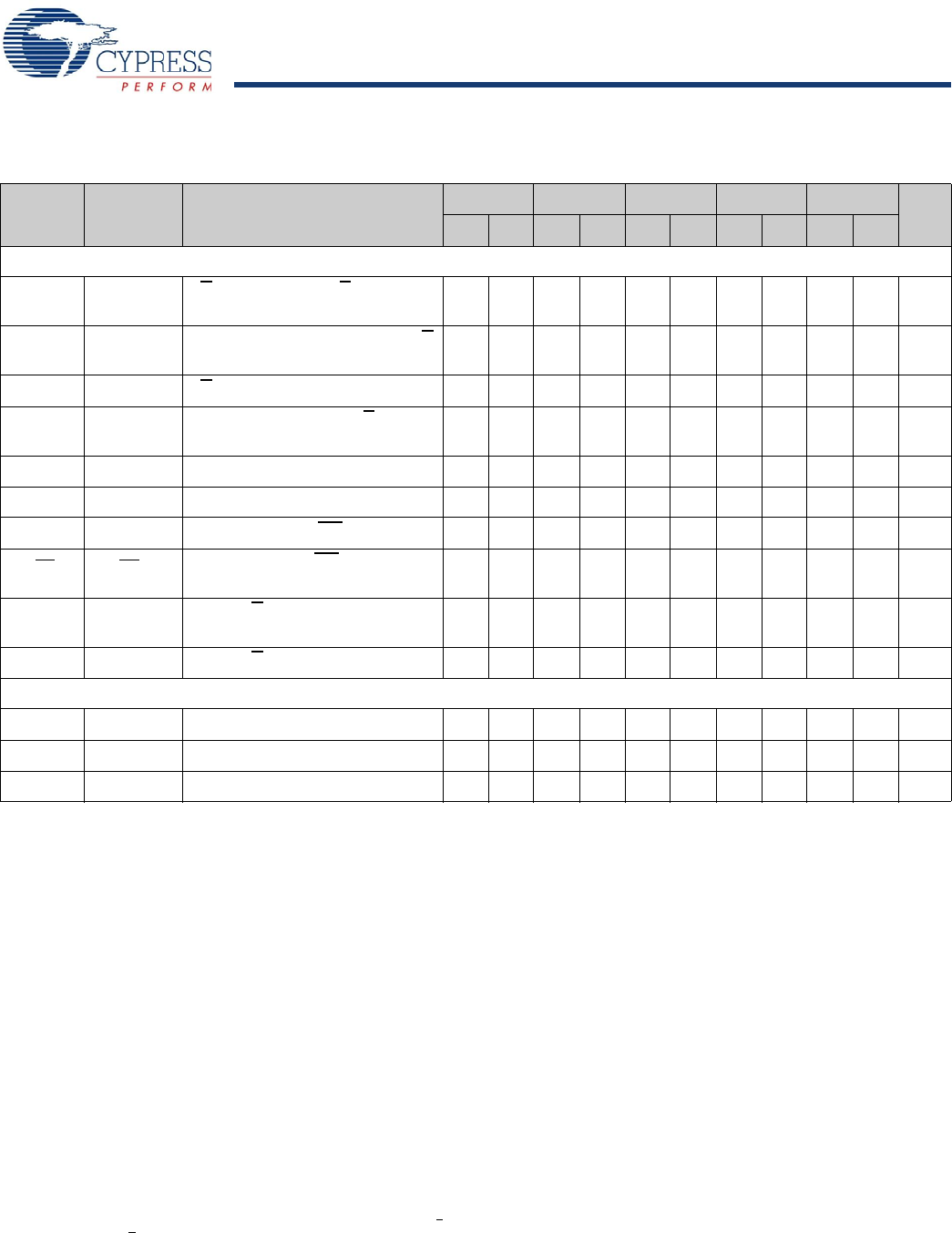

Output Times

t

CO

t

CHQV

C/C Clock Rise (or K/K in single

clock mode) to Data Valid

– 0.45 – 0.45 – 0.45 – 0.45 – 0.50 ns

t

DOH

t

CHQX

Data Output Hold after Output C/C

Clock Rise (Active to Active)

–0.45 – –0.45 – –0.45 – –0.45 – –0.50 – ns

t

CCQO

t

CHCQV

C/C Clock Rise to Echo Clock Valid – 0.45 – 0.45 – 0.45 – 0.45 – 0.50 ns

t

CQOH

t

CHCQX

Echo Clock Hold after C/C Clock

Rise

–0.45 – –0.45 – –0.45 – –0.45 – –0.50 – ns

t

CQD

t

CQHQV

Echo Clock High to Data Valid – 0.27 – 0.27 – 0.30 – 0.35 – 0.40 ns

t

CQDOH

t

CQHQX

Echo Clock High to Data Invalid –0.27 – –0.27 – –0.30 – –0.35 – –0.40 – ns

t

CQH

t

CQHCQL

Output Clock (CQ/CQ) HIGH

[24]

1.24–1.35–1.55–1.95–2.45– ns

t

CQHCQH

t

CQHCQH

CQ Clock Rise to CQ Clock Rise

(rising edge to rising edge)

[24]

1.24–1.35–1.55–1.95–2.45– ns

t

CHZ

t

CHQZ

Clock (C/C) Rise to High-Z

(Active to High-Z)

[25, 26]

– 0.45 – 0.45 – 0.45 – 0.45 – 0.50 ns

t

CLZ

t

CHQX1

Clock (C/C) Rise to Low-Z

[25, 26]

–0.45 – –0.45 – –0.45 – –0.45 – –0.50 – ns

DLL Timing

t

KC Var

t

KC Var

Clock Phase Jitter – 0.20 – 0.20 – 0.20 – 0.20 – 0.20 ns

t

KC lock

t

KC lock

DLL Lock Time (K, C) 1024 – 1024 – 1024 – 1024 – 1024 – Cycles

t

KC Reset

t

KC Reset

K Static to DLL Reset 30–30–30–30–30– ns

Switching Characteristics (continued)

Over the Operating Range

[20, 21]

Cypress

Parameter

Consortium

Parameter

Description

300 MHz 278 MHz 250 MHz 200 MHz 167 MHz

Unit

Min Max Min Max Min Max Min Max Min Max

Notes

24.These parameters are extrapolated from the input timing parameters (t

KHKH

- 250 ps, where 250 ps is the internal jitter. An input jitter of 200 ps (t

KC Var

) is already

included in the t

KHKH

). These parameters are only guaranteed by design and are not tested in production.

25.t

CHZ

, t

CLZ

are specified with a load capacitance of 5 pF as in (b) of AC Test Loads and Waveforms. Transition is measured ±100 mV from steady-state voltage.

26.At any voltage and temperature t

CHZ

is less than t

CLZ

and t

CHZ

less than t

CO

.

[+] Feedback