CY7C1346H

Document #: 38-05672 Rev. *B Page 16 of 16

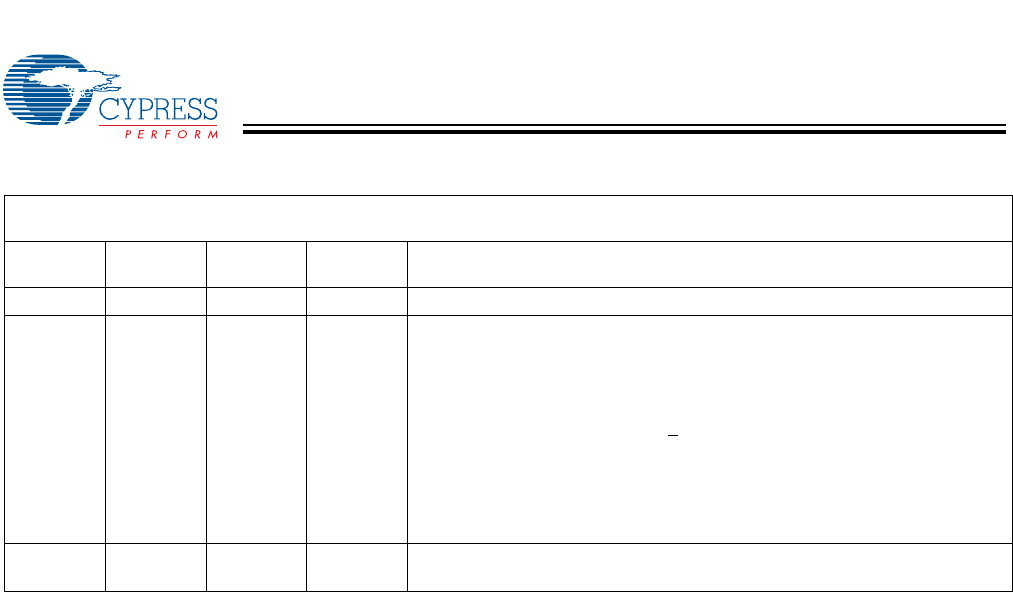

Document History Page

Document Title: CY7C1346H 2-Mbit (64K x 36) Pipelined Sync SRAM

Document Number: 38-05672

REV. ECN NO. Issue Date

Orig. of

Change Description of Change

** 347357 See ECN PCI New Data sheet

*A 420879 See ECN RXU Converted from Preliminary to Final.

Changed address of Cypress Semiconductor Corporation on Page# 1 from

“3901 North First Street” to “198 Champion Court”

Removed 133MHz Speed bin.

Changed three-state to tri-state.

Modified test condition from V

IH

< V

DD

to

V

IH

< V

DD

Modified “Input Load” to “Input Leakage Current except ZZ and MODE” in the

Electrical Characteristics Table.

Replaced Package Name column with Package Diagram in the Ordering

Information table.

Replaced Package Diagram of 51-85050 from *A to *B

*B 459347 See ECN NXR Included 2.5V I/O option

Updated the Ordering Information table.

[+] Feedback