CY7C1370DV25

CY7C1372DV25

Document #: 38-05558 Rev. *D Page 9 of 27

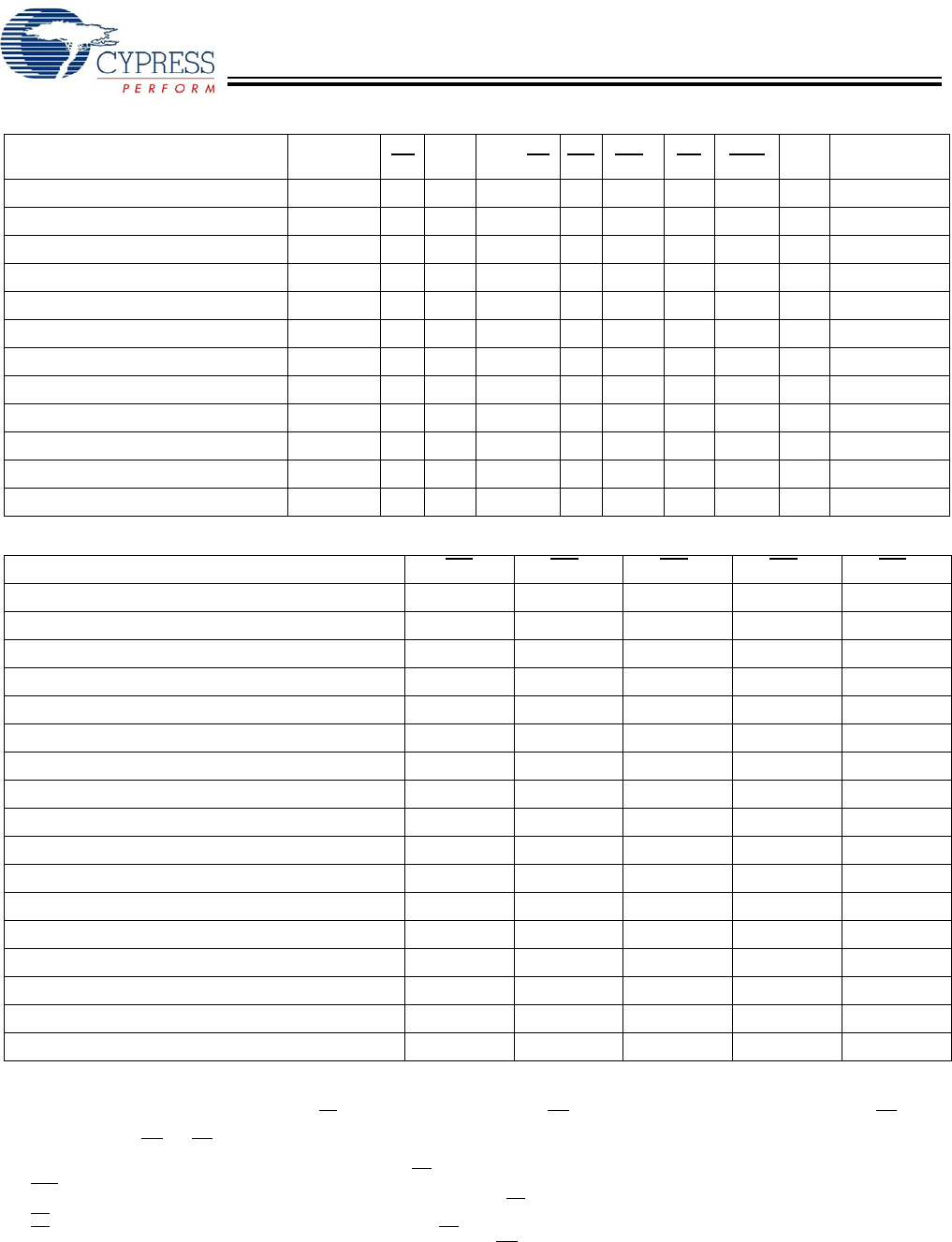

Truth Table

[1, 2, 3, 4, 5, 6, 7]

Operation

Address

Used CE ZZ ADV/LD WE BW

x

OE CEN CLK DQ

Deselect Cycle None H L L X X X L L-H Tri-state

Continue Deselect Cycle None X L H X X X L L-H Tri-state

Read Cycle (Begin Burst) External L L L H X L L L-H Data Out (Q)

Read Cycle (Continue Burst) Next X L H X X L L L-H Data Out (Q)

NOP/Dummy Read (Begin Burst) External L L L H X H L L-H Tri-state

Dummy Read (Continue Burst) Next X L H X X H L L-H Tri-state

Write Cycle (Begin Burst) External L L L L L X L L-H Data In (D)

Write Cycle (Continue Burst) Next X L H X L X L L-H Data In (D)

NOP/Write Abort (Begin Burst) None L L L L H X L L-H Tri-state

Write Abort (Continue Burst) Next X L H X H X L L-H Tri-state

Ignore Clock Edge (Stall) Current X L X X X X H L-H –

Sleep Mode None X H X X X X X X Tri-state

Partial Write Cycle Description

[1, 2, 3, 8]

Function (CY7C1370DV25) WE BW

d

BW

c

BW

b

BW

a

Read H X X X X

Write – No bytes written L H H H H

Write Byte a – (DQ

a

and

DQP

a

) LHHHL

Write Byte b – (DQ

b

and

DQP

b

)LHHLH

Write Bytes b, a L H H L L

Write Byte c – (DQ

c

and

DQP

c

)LHLHH

Write Bytes c, a L H L H L

Write Bytes c, b L H L L H

Write Bytes c, b, a L H L L L

Write Byte d – (DQ

d

and

DQP

d

)LLHHH

Write Bytes d, a L L H H L

Write Bytes d, b LLHLH

Write Bytes d, b, a L L H L L

Write Bytes d, c L L L H H

Write Bytes d, c, a L L L H L

Write Bytes d, c, b L L L L H

Write All Bytes L L L L L

Notes:

1. X = “Don't Care”, H = Logic HIGH, L = Logic LOW, CE

stands for ALL Chip Enables active. BWx = L signifies at least one Byte Write Select is active, BW

x

= Valid

signifies that the desired byte write selects are asserted, see Write Cycle Description table for details.

2. Write is defined by WE

and BW

X

. See Write Cycle Description table for details.

3. When a write cycle is detected, all I/Os are tri-stated, even during byte writes.

4. The DQ and DQP pins are controlled by the current cycle and the OE

signal.

5. CEN

= H inserts wait states.

6. Device will power-up deselected and the I/Os in a tri-state condition, regardless of OE

.

7. OE

is asynchronous and is not sampled with the clock rise. It is masked internally during write cycles.During a read cycle DQ

s

and DQP

X

= Three-state when

OE

is inactive or when the device is deselected, and DQ

s

= data when OE is active.

8. Table only lists a partial listing of the byte write combinations. Any Combination of BW

X

is valid. Appropriate write will be done based on which byte write is active.

[+] Feedback