CY7C1380D, CY7C1382D

CY7C1380F, CY7C1382F

Document #: 38-05543 Rev. *F Page 9 of 34

Burst Sequences

The CY7C1380D/CY7C1382D/CY7C1380F/CY7C1382F

provides a two-bit wraparound counter, fed by A1: A0, that imple-

ments an interleaved or a linear burst sequence. The interleaved

burst sequence is designed specifically to support Intel Pentium

applications. The linear burst sequence is designed to support

processors that follow a linear burst sequence. The burst

sequence is user selectable through the MODE input.

Asserting ADV

LOW at clock rise automatically increments the

burst counter to the next address in the burst sequence. Both

read and write burst operations are supported.

Sleep Mode

The ZZ input pin is an asynchronous input. Asserting ZZ places

the SRAM in a power conservation sleep mode. Two clock cycles

are required to enter into or exit from this sleep mode. While in

this mode, data integrity is guaranteed. Accesses pending when

entering the sleep mode are not considered valid nor is the

completion of the operation guaranteed. The device must be

deselected prior to entering the sleep mode. CE

1

, CE

2

, CE

3

,

ADSP

, and ADSC must remain inactive for the duration of t

ZZREC

after the ZZ input returns LOW.

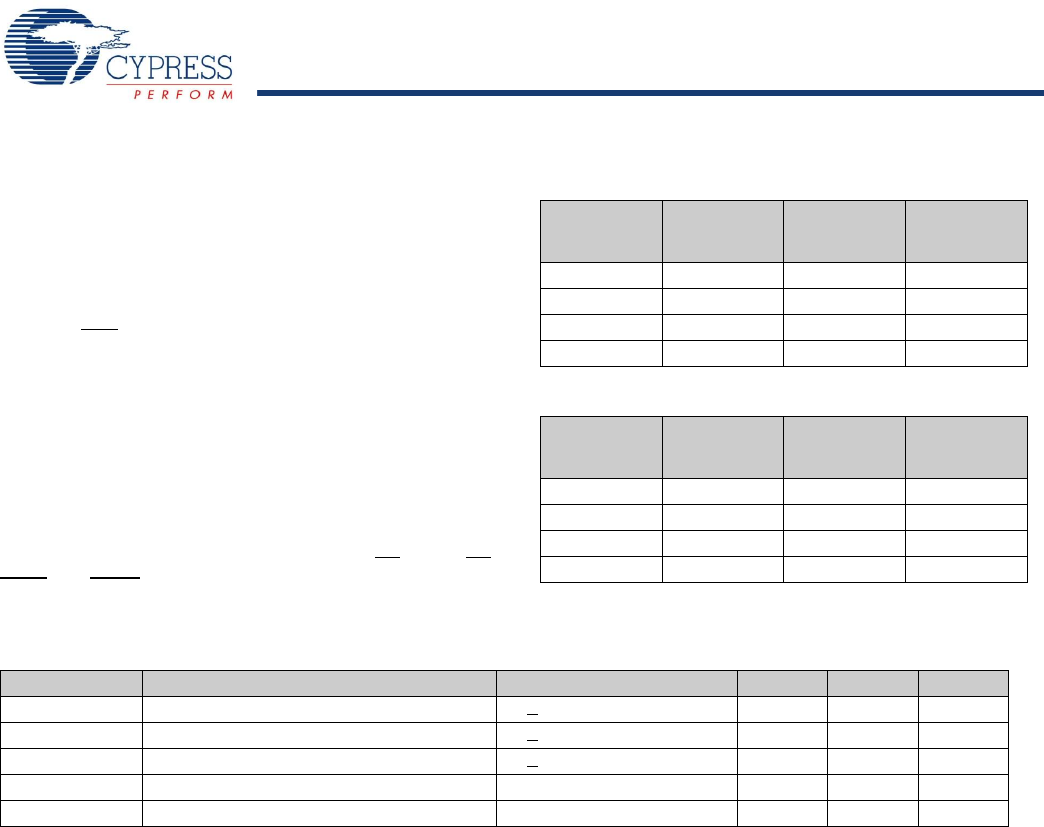

Table 2. Interleaved Burst Address Table (MODE = Floating

or VDD)

First

Address

A1: A0

Second

Address

A1: A0

Third

Address

A1: A0

Fourth

Address

A1: A0

00 01 10 11

01 00 11 10

10 11 00 01

11 10 01 00

Table 3. Linear Burst Address Table (MODE = GND)

First

Address

A1: A0

Second

Address

A1: A0

Third

Address

A1: A0

Fourth

Address

A1: A0

00 01 10 11

01 10 11 00

10 11 00 01

11 00 01 10

Table 4. ZZ Mode Electrical Characteristics

Parameter Description Test Conditions Min Max Unit

I

DDZZ

Sleep mode standby current ZZ > V

DD

– 0.2V 80 mA

t

ZZS

Device operation to ZZ ZZ > V

DD

– 0.2V 2t

CYC

ns

t

ZZREC

ZZ recovery time ZZ < 0.2V 2t

CYC

ns

t

ZZI

ZZ Active to sleep current This parameter is sampled 2t

CYC

ns

t

RZZI

ZZ Inactive to exit sleep current This parameter is sampled 0 ns

[+] Feedback