CY7C1386DV25, CY7C1386FV25

CY7C1387DV25, CY7C1387FV25

Document Number: 38-05548 Rev. *E Page 14 of 30

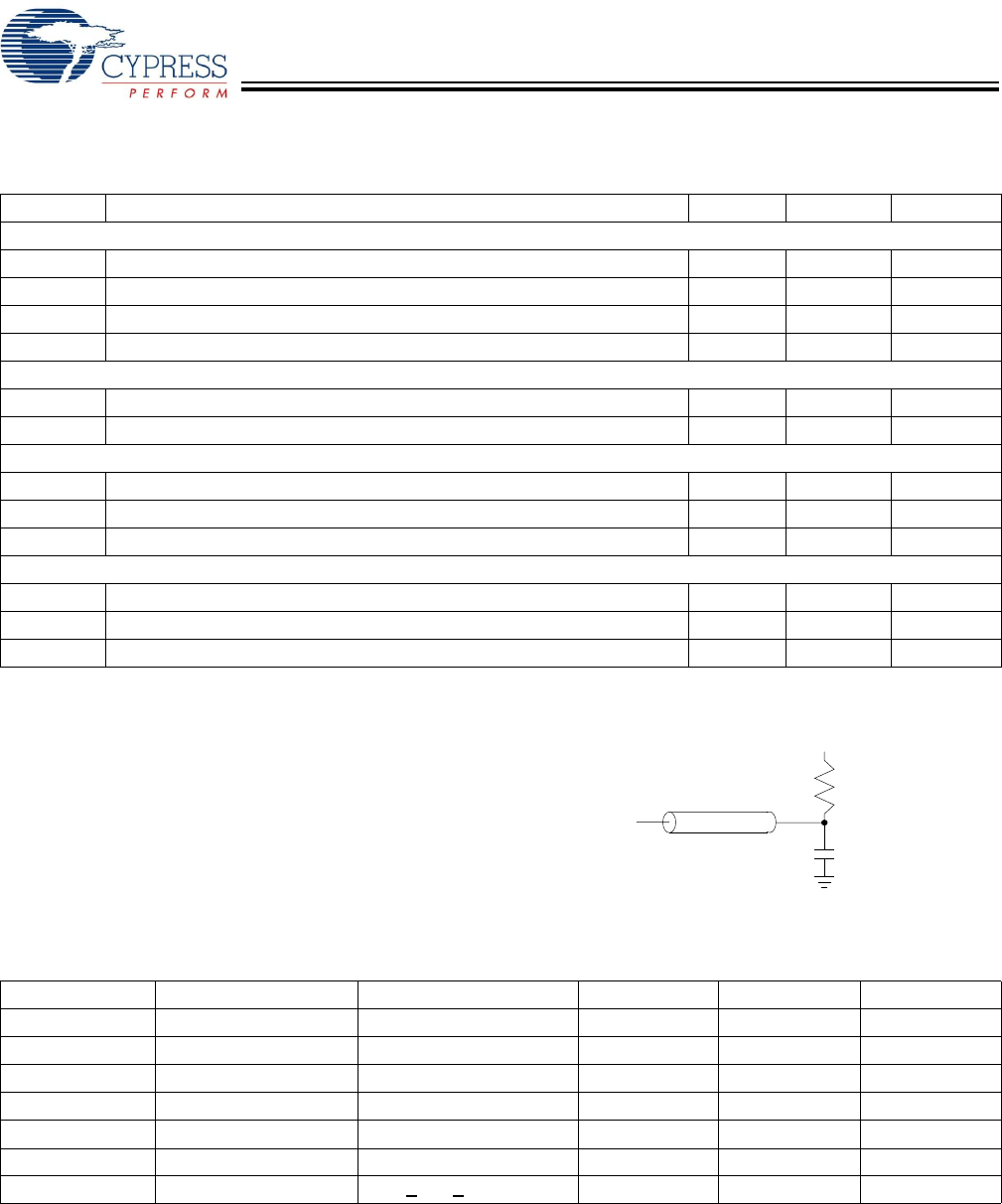

TAP AC Test Conditions

Input pulse levels.................................................V

SS

to 2.5V

Input rise and fall time..................................................... 1 ns

Input timing reference levels.........................................1.25V

Output reference levels.................................................1.25V

Test load termination supply voltage.............................1.25V

TAP AC Output Load Equivalent

TAP AC Switching Characteristics

Over the Operating Range

[11, 12]

Parameter Description Min. Max. Unit

Clock

t

TCYC

TCK Clock Cycle Time 50 ns

t

TF

TCK Clock Frequency 20 MHz

t

TH

TCK Clock HIGH time 20 ns

t

TL

TCK Clock LOW time 20 ns

Output Times

t

TDOV

TCK Clock LOW to TDO Valid 10 ns

t

TDOX

TCK Clock LOW to TDO Invalid 0 ns

Setup Times

t

TMSS

TMS Setup to TCK Clock Rise 5 ns

t

TDIS

TDI Setup to TCK Clock Rise 5 ns

t

CS

Capture Setup to TCK Rise 5 ns

Hold Times

t

TMSH

TMS Hold after TCK Clock Rise 5 ns

t

TDIH

TDI Hold after Clock Rise 5 ns

t

CH

Capture Hold after Clock Rise 5 ns

TDO

1.25V

20pF

Z = 50 Ω

O

50Ω

TAP DC Electrical Characteristics And Operating Conditions

(0°C < TA < +70°C; V

DD

= 2.5V ±0.165V unless otherwise noted)

[13]

Parameter Description Test Conditions Min. Max. Unit

V

OH1

Output HIGH Voltage I

OH

= –1.0 mA 1.7 V

V

OH2

Output HIGH Voltage I

OH

= –100 µA 2.1 V

V

OL1

Output LOW Voltage I

OL

= 1.0 mA 0.4 V

V

OL2

Output LOW Voltage I

OL

= 100 µA 0.2 V

V

IH

Input HIGH Voltage 1.7 V

DD

+ 0.3 V

V

IL

Input LOW Voltage –0.3 0.7 V

I

X

Input Load Current GND < V

IN

< V

DDQ

–5 5 µA

Note

11. t

CS

and t

CH

refer to the setup and hold time requirements of latching data from the boundary scan register.

12.Test conditions are specified using the load in TAP AC test conditions. t

R

/t

F

= 1ns.

13.All voltages referenced to V

SS

(GND).

[+] Feedback