CY7C1460AV33

CY7C1462AV33

CY7C1464AV33

Document #: 38-05353 Rev. *D Page 13 of 27

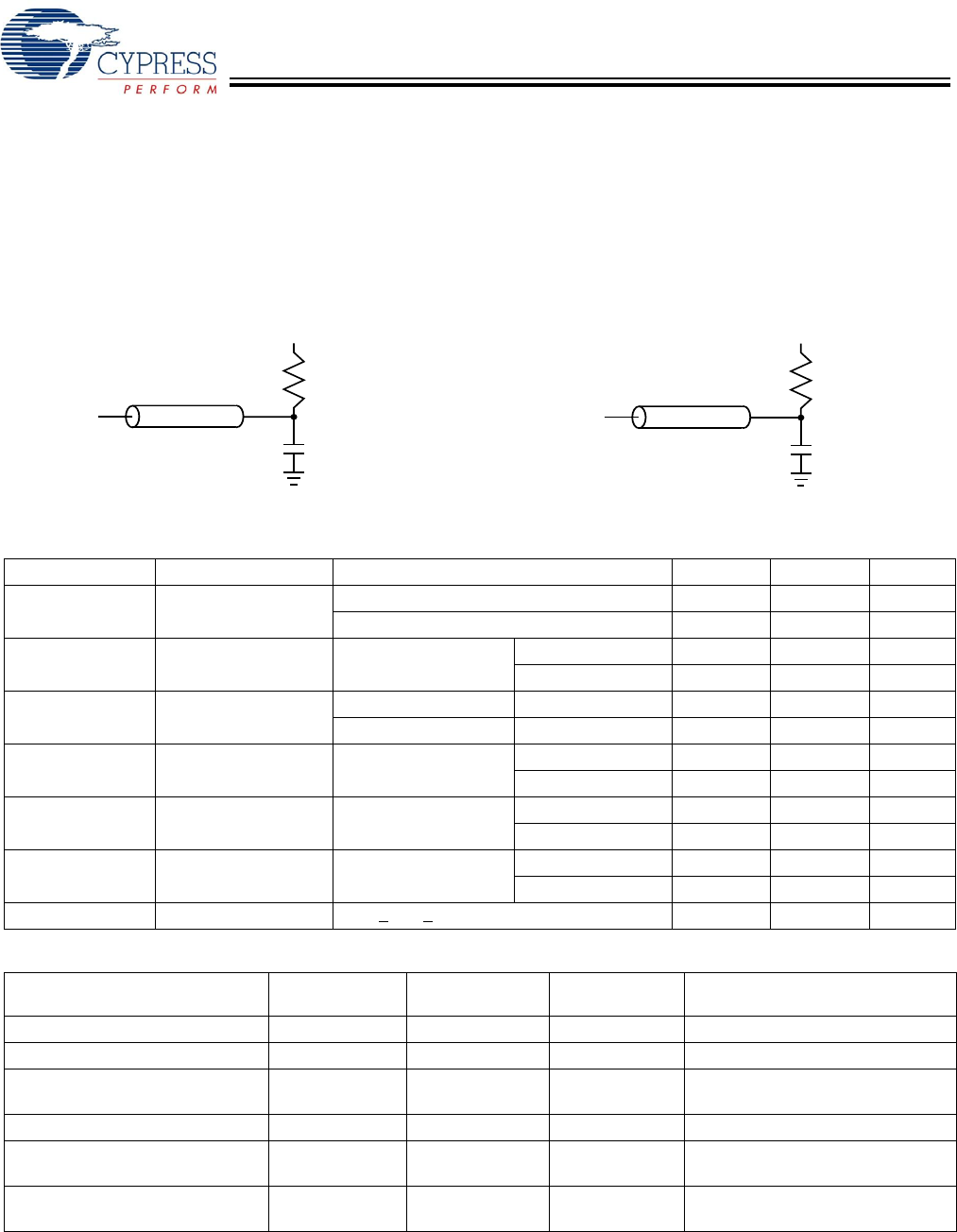

3.3V TAP AC Test Conditions

Input pulse levels ................................................ V

SS

to 3.3V

Input rise and fall times................................................... 1 ns

Input timing reference levels...........................................1.5V

Output reference levels...................................................1.5V

Test load termination supply voltage...............................1.5V

3.3V TAP AC Output Load Equivalent

2.5V TAP AC Test Conditions

Input pulse levels ................................................V

SS

to 2.5V

Input rise and fall time .....................................................1 ns

Input timing reference levels......................................... 1.25V

Output reference levels ................................................1.25V

Test load termination supply voltage ............................1.25V

2.5V TAP AC Output Load Equivalent

T

DO

1.5V

20p

F

Z = 50Ω

O

50Ω

T

DO

1.25V

20p

F

Z = 50Ω

O

50Ω

TAP DC Electrical Characteristics And Operating Conditions

(0°C < TA < +70°C; V

DD

= 3.135V to 3.6V unless otherwise noted)

[11]

Parameter Description Test Conditions Min. Max. Unit

V

OH1

Output HIGH Voltage I

OH

= –4.0 mA, V

DDQ

= 3.3V 2.4 V

I

OH

= –1.0 mA, V

DDQ

= 2.5V 2.0 V

V

OH2

Output HIGH Voltage I

OH

= –100 µA V

DDQ

= 3.3V 2.9 V

V

DDQ

= 2.5V 2.1 V

V

OL1

Output LOW Voltage I

OL

= 8.0 mA V

DDQ

= 3.3V 0.4 V

I

OL

= 1.0 mA V

DDQ

= 2.5V 0.4 V

V

OL2

Output LOW Voltage I

OL

= 100 µA V

DDQ

= 3.3V 0.2 V

V

DDQ

= 2.5V 0.2 V

V

IH

Input HIGH Voltage V

DDQ

= 3.3V 2.0 V

DD

+ 0.3 V

V

DDQ

= 2.5V 1.7 V

DD

+ 0.3 V

V

IL

Input LOW Voltage V

DDQ

= 3.3V –0.3 0.8 V

V

DDQ

= 2.5V –0.3 0.7 V

I

X

Input Load Current GND < V

IN

< V

DDQ

–5 5 µA

Identification Register Definitions

Instruction Field

CY7C1460AV33

(1M ×36)

CY7C1462AV33

(2M ×18)

CY7C1464AV33

(512K ×72) Description

Revision Number (31:29) 000 000 000 Describes the version number.

Device Depth (28:24)

[12]

01011 01011 01011 Reserved for Internal Use

Architecture/Memory Type(23:18) 001000 001000 001000 Defines memory type and archi-

tecture

Bus Width/Density(17:12) 100111 010111 110111 Defines width and density

Cypress JEDEC ID Code (11:1) 00000110100 00000110100 00000110100 Allows unique identification of

SRAM vendor.

ID Register Presence Indicator (0) 1 1 1 Indicates the presence of an ID

register.

Notes:

11. All voltages referenced to V

SS

(GND).

12.Bit #24 is “1” in the ID Register Definitions for both 2.5V and 3.3V versions of this device.

[+] Feedback