CY7C1470V25

CY7C1472V25

CY7C1474V25

Document #: 38-05290 Rev. *I Page 27 of 28

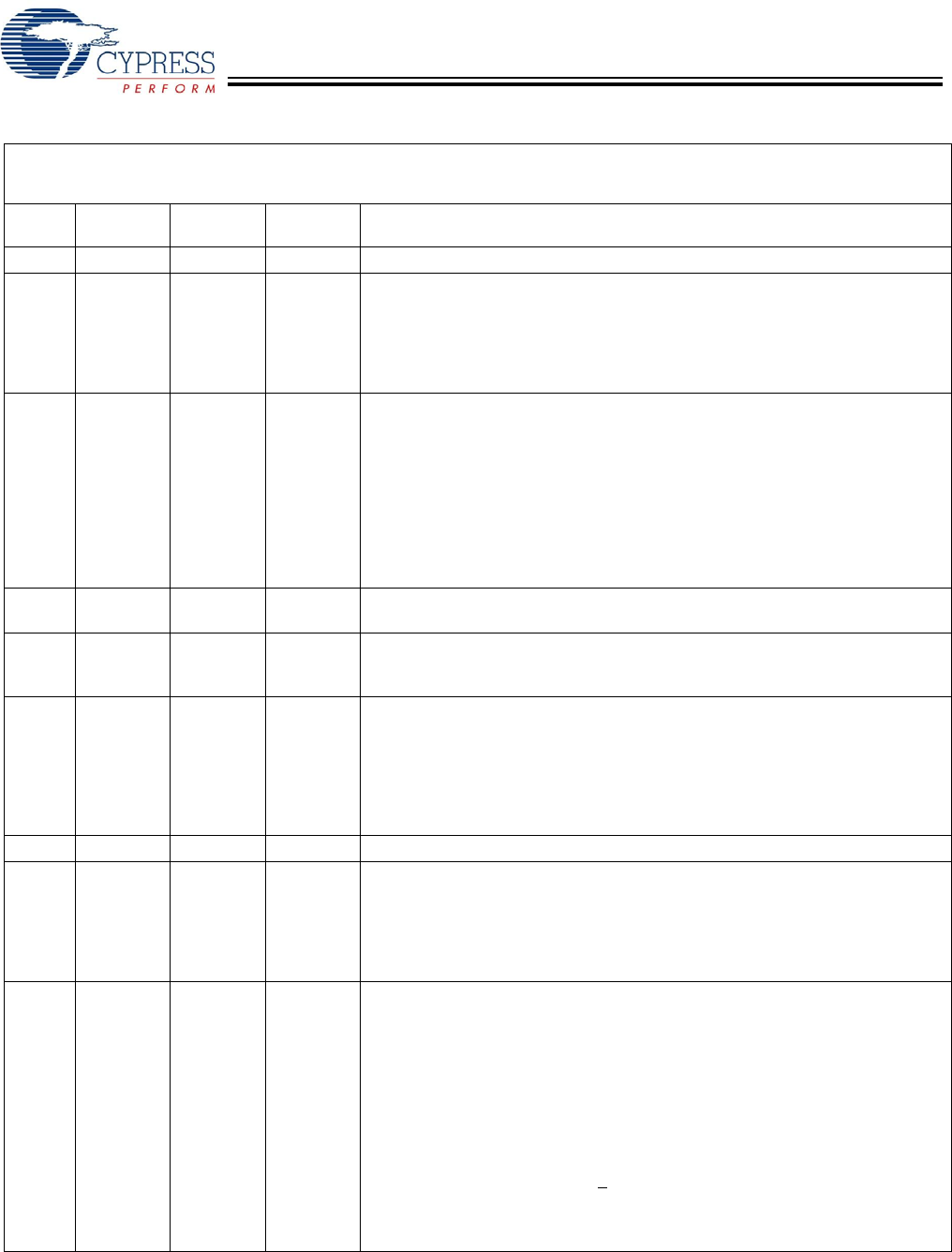

Document History Page

Document Title: CY7C1470V25/CY7C1472V25/CY7C1474V25 72-Mbit(2M x 36/4M x 18/1M x 72)

Pipelined SRAM with NoBL™ Architecture

Document Number: 38-05290

REV. ECN No. Issue Date

Orig. of

Change Description of Change

** 114677 08/06/02 PKS New data sheet

*A 121519 01/27/03 CJM Updated features for package offering

Removed 300-MHz offering

Changed tCO, tEOV, tCHZ, tEOHZ from 2.4 ns to 2.6 ns (250 MHz), tDOH, tCLZ

from 0.8 ns to 1.0 ns (250 MHz), tDOH, tCLZ from 1.0 ns to 1.3 ns (200 MHz)

Updated ordering information

Changed Advanced Information to Preliminary

*B 223721 See ECN NJY Changed timing diagrams

Changed logic block diagrams

Modified Functional Description

Modified “Functional Overview” section

Added boundary scan order for all packages

Included thermal numbers and capacitance values for all packages

Included IDD and ISB values

Removed 250-MHz offering and included 225-MHz speed bin

Changed package outline for 165FBGA package and 209-ball BGA package

Removed 119-BGA package offering

*C 235012 See ECN RYQ Minor Change: The data sheets do not match on the spec system and

external web

*D 243572 See ECN NJY Changed ball C11,D11,E11,F11,G11 from DQPb,DQb,DQb,DQb,DQb to

DQPa,DQa,DQa,DQa,DQa in page 4

Modified capacitance values in page 19

*E 299511 See ECN SYT Removed 225-MHz offering and included 250-MHz speed bin

Changed t

CYC

from 4.4 ns to 4.0 ns for 250-MHz Speed Bin

Changed Θ

JA

from 16.8 to 24.63 °C/W and Θ

JC

from 3.3 to 2.28 °C/W for 100

TQFP Package on Page # 19

Added lead-free information for 100-Pin TQFP and 165 FBGA Packages

Added comment of ‘Lead-free BG packages availability’ below the Ordering

Information

*F 320197 See ECN PCI Corrected typo in part numbers on page# 9 and 10

*G 331513 See ECN PCI Address expansion pins/balls in the pinouts for all packages are modified as per

JEDEC standard

Added Address Expansion pins in the Pin Definitions Table

Added Industrial Operating Range

Modified V

OL

, V

OH

Test Conditions

Updated Ordering Information Table

*H 416221 See ECN RXU Converted from Preliminary to Final

Changed address of Cypress Semiconductor Corporation on Page# 1 from

“3901 North First Street” to “198 Champion Court”

Changed Three-state to Tri-state

Changed the description of I

X

from Input Load Current to Input Leakage Current

on page# 17

Changed the I

X

current values of MODE on page # 17 from –5 µA and 30 µA

to –30 µA and 5 µA

Changed the I

X

current values of ZZ on page # 17 from –30 µA and 5 µA

to –5 µA and 30 µA

Changed V

DDQ

< V

DD

to V

DDQ

< V

DD

on page #17

Replaced Package Name column with Package Diagram in the Ordering Infor-

mation table

Updated Ordering Information table

[+] Feedback